分裂平面和当微带信号穿过它们时会发生什么

你不知道你不知道的事情会毁了你的一天。本文通过详细的实例说明,在高速设计的今天,我们不能再仅仅局限于信号完整性、功率完整性或电磁兼容。我们必须考虑所有这三个学科,并对它们中的每一个都进行教育,以实现成功的设计。

当讨论信号完整性(SI)问题时,当印刷电路板(PCB)的一层上的信号在相邻层的参考平面上跨越分裂或插槽时,总是存在很大的争论。一方面,一些人认为不应该越过分割平面,因为这会增加串扰的风险,并可能无法通过电磁兼容性(EMC)法规。另一方面,也有人强调,如果电路间隙的宽度和电源/接地层设计得很仔细,这可能不是一个大问题。那么谁是对的呢?

就像所有涉及信号完整性的事情一样,答案是,“这要看情况了。”最好的回答方式是“看情况”就是输入数字。本文试图消除一些关于信号穿过分裂平面的神话。

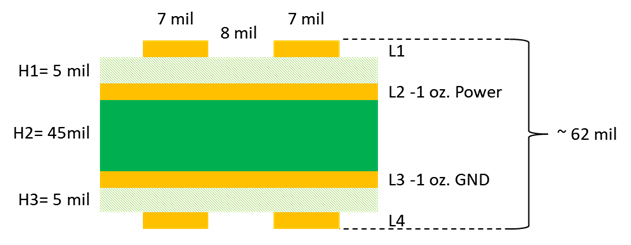

首先,让我们看看一个典型的4层PCB ~ 62密耳厚,如图1所示的堆叠。外两层为微带信号层,内两层为电源层和地层。痕迹宽度为7密耳宽,间隔为8密耳。差分驱动时阻抗为~100欧姆;信号端驱动时,阻抗为~ 56欧姆。

图1简单的4层PCB堆叠

在现代设计中,有多个电源轨是很常见的。在4层板上,这意味着功率层通常会被分割,因此,在相邻参考平面上穿越分割或插槽的走线通常是不可避免的。

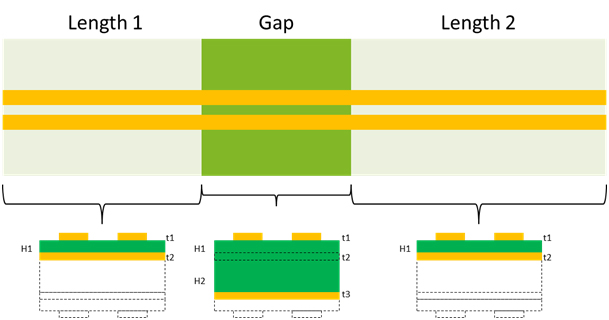

假设我们在顶层上有一对走线,穿过相邻层上50mil的间隙,如图2所示。缝隙前后微带截面的横截面为顶层至功率参考平面的介电厚度(H1)。由于间隙段在相邻的电源层上没有参考平面,所以下一个参考平面是与底层相邻的GND层。因此,间隙上的介电厚度等于H1的厚度加上1盎司功率层的厚度(t2)加上下一介电层的厚度(H2)。如果1盎司功率层的厚度为1.2密耳,则电介质的总厚度为51.2密耳。

这种拓扑的一阶近似是具有两个不同阻抗的三个传输线段的组合。第一段和最后段的差分阻抗为100欧姆,SE为56欧姆,而间隙上的走线阻抗为~134欧姆的差分阻抗和~103欧姆的SE。由于跨越间隙的阻抗高于第一段和最后段,我们期望看到在间隙长度上的正反射。反射的高度和宽度将是上升时间和间隙几何形状的函数。快速上升时间和较长的间隙比缓慢上升时间和较短的间隙给出更高的反射。

图2相对于间隙模型拓扑的横截面几何形状

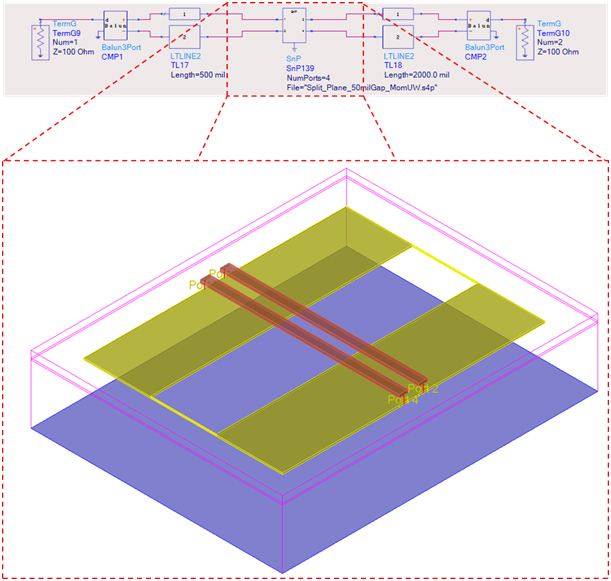

为了了解这个问题有多严重,我们可以使用Keysight ADS[1]快速建模和模拟,如图3所示。利用内部二维场求解器对间隙段前后的两个传输线段进行了建模。TLines-Line类型“托盘。为了准确捕捉信号穿过间隙时的电磁效应,利用动量三维平面场求解器对间隙段进行了建模和仿真。它们都有相同的底物定义。动量的s参数结果以试金石格式保存,并带回ADS示意图。

拓扑图的总长度为2.650英寸。第一部分,长度是1是500毫升,最后一部分,长度2是2英寸。3D模型部分被分成三个50 mil的部分,以方便间隙调整,并确保总长度保持不变。

选择两种间隙长度来比较小间隙和大间隙。在动力平面之间有50毫米的间隔并不罕见,所以这就是最坏情况下的差距。在最佳情况下,选择5密耳的间隙,这是迹线到垫片间隙规格的典型最小值。

图3 Keysight ADS通用原理图用于建模和模拟微带分裂平面

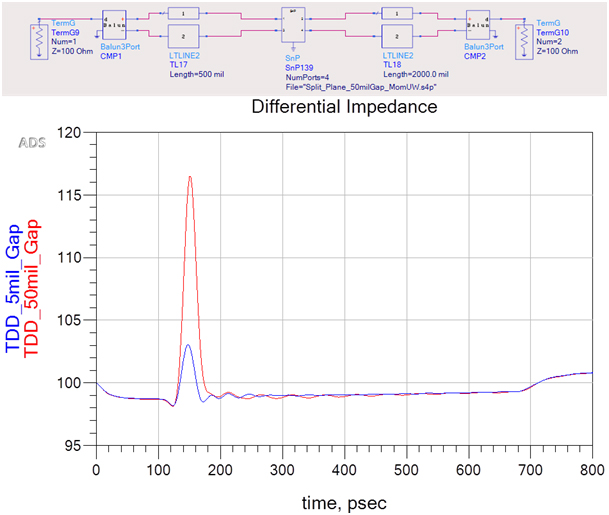

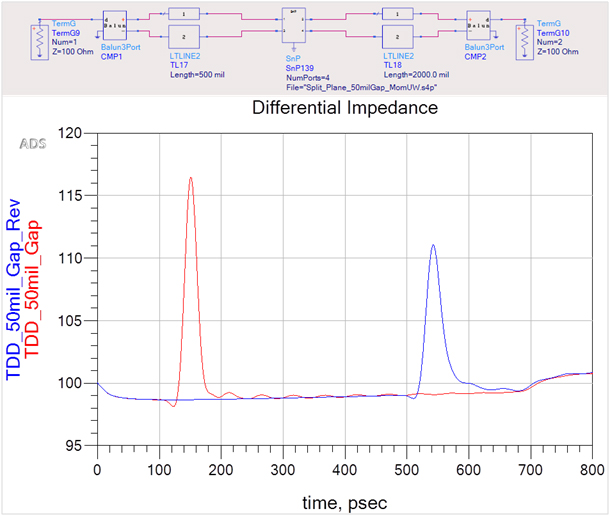

当拓扑从端口1差分驱动时,差分阻抗的比较如图4所示。为了方便,使用Balun变压器从4端口转换为2端口。正如预期的那样,对于红色所示的50mil间隙,比蓝色所示的5mil间隙有更高的阻抗不连续。

这是因为反射脉冲的高度是由上升时间的空间长度和间隙宽度的组合决定的。由于上升时间的空间长度小于间隙宽度,因此它永远不会达到阻抗不连续的全部幅度。

图4 50mil间隙(红色)与5mil间隙(蓝色)的差分阻抗比较

为了证明这一点,我们可以从端口2驱动50 mil间隙拓扑,并将其与端口1进行比较,如图5所示。由于边缘在到达间隙之前必须传播2.05英寸,因此由于有损耗的传输线引起的色散,它的速度较慢。果然,正如我们预测的那样,反射的强度要低一些。

图5两端驱动时带50mil间隙拓扑的差分阻抗。由色散引起的较慢的上升时间导致2.05英寸(蓝色)后的反射较少,而550密尔(红色)后的反射较高。

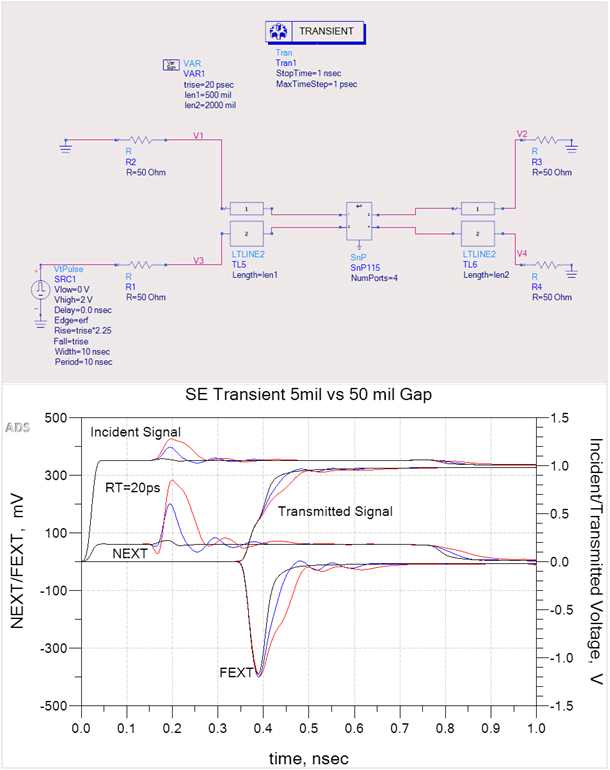

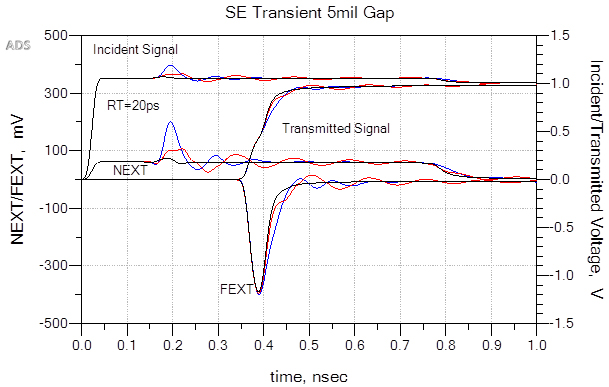

接下来,进行单端(SE)瞬态分析,结果如图6所示。红色区域的间隔为50英里。蓝色的区域间隔为5英里。黑色的地块没有缝隙。入射信号的上升时间为20ps,显示了与无间隙相比在各自间隙处的反射电压。正如预期的那样,这是5000万美元差距中最高的。在50mil间隙中,传输信号的上升时间衰减增加,导致传输延迟略有增加。

该图还显示了所有三种情况下的经典近端串音(NEXT)和远端串音(ext)签名。由于穿过间隙的迹线的紧密耦合,较高的入射反射表现为较高的NEXT。

图6单端入射/发射信号对比,NEXT/ ext为5 mil间隙(蓝色图);50米(红色图);没有缝隙(黑色图)。由于穿过间隙的迹线的紧密耦合,较高的入射反射表现为较高的NEXT,但两种情况下的ext幅度都很少增加。

尽管在50 mil间隙中,NEXT脉冲显著增加,但与没有间隙相比,两种情况下的ext幅度几乎没有增加。与NEXT电压不同,ext电压的峰值随耦合长度的变化而变化。在一定的延时(TD)下,当其振幅增长到与侵略者上升时间的50%的电压相当的水平时,它达到峰值。

以同样的方式,攻击波形将ext电压耦合到受害者上,而ext将噪声耦合回攻击波形,影响上升时间,如图所示。由于叠加,远端的干扰波形是ext电压和原始传输波形的总和,而原始传输波形将出现在TD处,没有耦合。由于远端距离为2.65英寸,ext接近饱和。

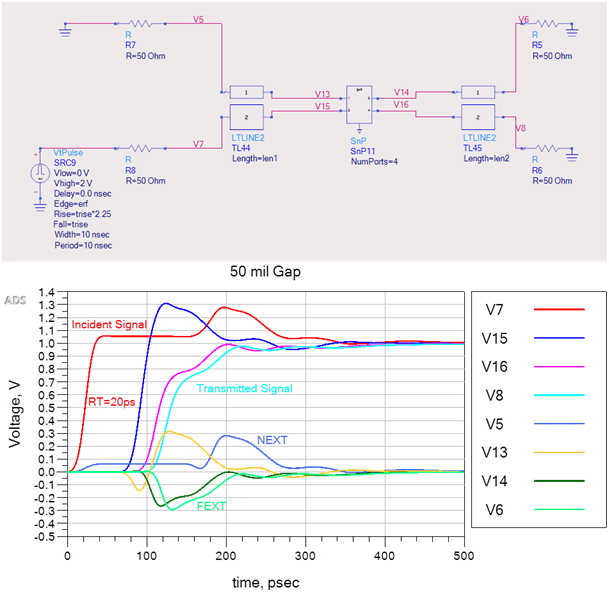

如果我们将最后一个传输线段(TL45)减少到100 mil,然后在间隙段(SnP11)前后进行探测,如图7所示,我们可以更好地理解间隙对ext的影响。

红色图为入射信号(V7),上升时间为20ps。青色图为远端发射信号(V8)。浅蓝色的图是V5的NEXT,浅绿色的图是远端的ext (V6)。深蓝色图(V15)为TL44后的发射信号,为V13节点的攻击信号。由于间隙部分在间隙上具有更高的特性阻抗,因此我们观察到由于间隙长度的反射增加而引起的超调。

橙色图(V13)显示负的ext脉冲,与V15侵略者的上升沿一致。它还显示增加的NEXT脉冲与V15上的正反射相一致。当侵略者信号通过间隙段传播时,反射的附加电压摆幅增加了ext脉冲的幅度,反向形状反映了反射脉冲的形状,如图(V14)所示。然后,ext脉冲耦合回侵略信号,并在其离开耦合段时降低上升时间,如品红色图(V16)所示。

入侵信号通过最后一段传输线(TL45)传播后,ext脉冲的幅度与长度成正比。在这种情况下,它没有最大化,因为最后一段只有100密耳。

结论是,当信号穿过分割平面时,传输信号会出现阻抗失配,导致正反射的时间等于间隙的长度,这增加了FEXT脉冲的幅度和形状,从而降低了与FEXT脉冲形状成比例的传输信号的上升时间。

图7显示NEXT/ ext和各节点传输信号的单端瞬态响应。

劈裂面和沿劈裂边分流的返回电流的结合产生了一个有效的缝隙天线,它将辐射噪声。满足FCC B类3米辐射发射;在30 ~ 88mhz范围内,辐射噪声必须小于100微伏/米;在216mhz ~ 1ghz范围内,辐射噪声必须小于200微伏/米。在这些低电压水平下,不需要太多电流就能使EMC失效。

由于微带几何中走线的返回电流在穿过分割平面时是不连续的,因此产生的任何噪声都将辐射到自由空间中,因为在走线上方没有屏蔽层来容纳它。我们可以在相邻参考平面上可视化返回当前行为,因为它穿过分割使用动量3D查看器。

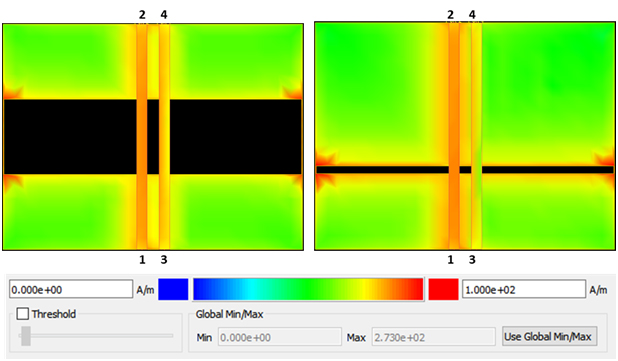

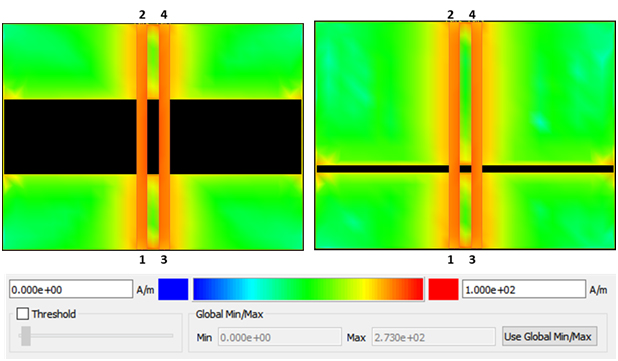

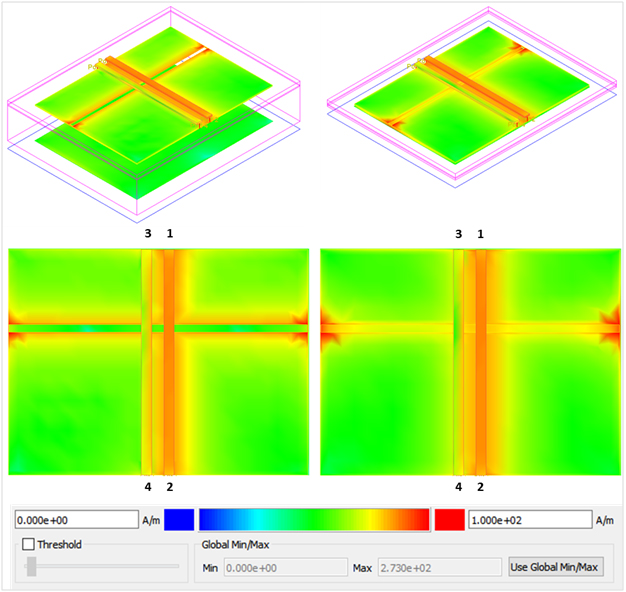

图8比较了当4 GHz正弦波信号穿过左侧50 mil间隙和右侧5 mil间隙时SE返回电流密度在参考平面上的表现。选择这个频率是因为它是我们可能在典型的4层PCIe板上发现的8 GT/s PCIe Gen 3链路的奈奎斯特频率。当一条走线从端口1驱动到端口2,而端口3和端口4被终止时,我们可以清楚地看到参考平面上的返回电流密度在分裂时的行为。

我们注意到沿断裂处受害者痕迹边缘的电流密度略有增加。这表明一些电流返回相邻的迹线,这说明了前面讨论的额外的NEXT脉冲。仅从这张图来看,用单端驱动迹线穿过分割平面可能不是一个好主意。

图8当4GHz SE信号穿过50mil间隙(左)和5mil间隙(右)时,返回电流密度在参考平面上的表现示例。

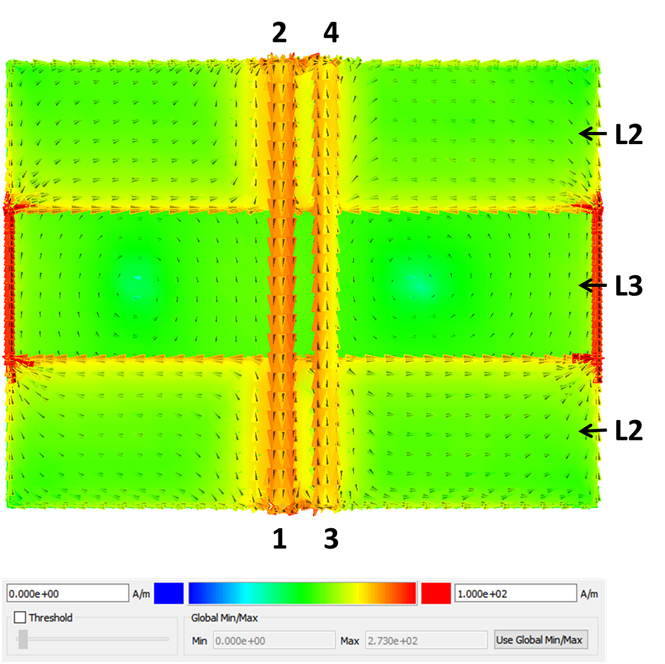

图9比较了当4 GHz信号穿过左边50 mil间隙和右边5 mil间隙时,差分返回电流密度在参考平面上的表现。我们可以看到,最大电流密度集中在差分对之间的平面分裂边缘,少量沿着分裂扩散。

图9当4GHz差分正弦波穿过50mil间隙(左)和5mil间隙(右)时,返回电流密度在参考平面上的表现示例。

图10显示了连接端口1-2的走线为单端驱动,另一走线为端接时,L2和L3平面层上的电流流向。我们观察到,当电流方向从走线上的端口2到端口1时,L2上的返回电流在到达间隙的远端(端口1侧)时分裂为左和右。然后,它绕过间隙,在跟踪下返回到端口2。

我们还观察到L3上有两个反向旋转电流。它们大约集中在空隙的左右两半。它们是由于沿L2上间隙边缘的反向旋转电流将EM能量注入平面腔而引起的。我们注意到L2上的电流旋转方向与L3相反。

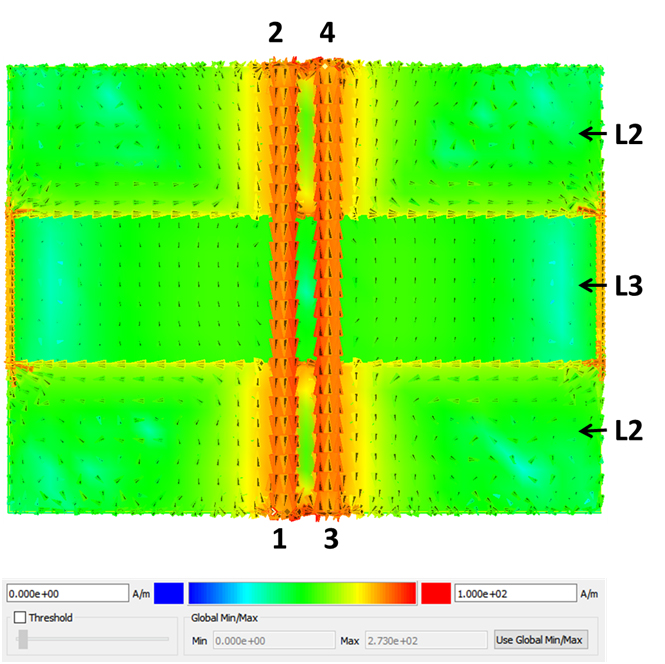

但是当两条走线被差分驱动时,如图11所示,我们看到沿每一半间隙的电流方向相同。我们还注意到,电流的旋转在L3上是一个方向的,在差分对之间的中心和间隙的中间。

结论是,即使两条走线被差分驱动,仍然有电流沿着间隙边缘流动,这会将噪声注入腔体并辐射到自由空间,从而产生EMI。

图10连接端口1到端口2的走线为单端驱动,而另一端的走线分别在两端终止时,参考平面L2和L3上的回流电流。

图11两条走线采用差分驱动时参考平面L2和L3上的回流电流

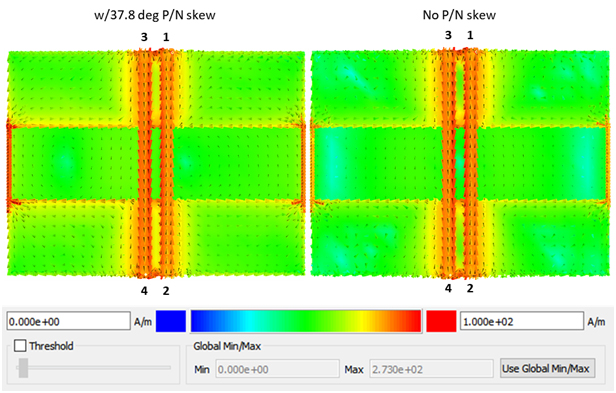

到目前为止,我们所分析的差分对场景假设了一个完美的对内倾斜匹配。但在现实生活中,这种情况很少发生。当差分走线改变层时,布线长度不匹配、纤维编织效应、连接器引脚长度差异或回孔位置不对称等问题将导致对内倾斜。当这种情况发生时,一些差分信号被转换为公共信号,如图12所示。这个量是相对于有多少内对倾斜。

在完全平衡的差分对中,Vdiff是P/N信号之间的电压差。如果它们恰好180度相反,则产生的差分电压是两倍,并且没有共同电压。

有一个斜的瞬间;它们不再是180度相异。当取差值时,差分信号失真并产生一个公共电压(Vcom)。Vcom的大小和形状与相移量成正比。当P和N恰好同相时,差电压为0%,共电压为100%。

由此产生的公共电压也需要电流返回路径,如果它被中断,它的返回电流表现为单端返回电流穿过分裂平面。

图12由于P/N相移引起的差分信号到共信号的转换称为偏斜。

PCIe外部布线规范,Revision 1.0[2]最坏情况的倾斜预算是单位间隔(U.I.)的21%,其中一个U.I.等于位时间。使用0.21 UI为PCIe gen 3在8GT/s,这是26.3ps。

通过对50 mil间隙模型应用等效的37.8度对内相移,将结果与平衡情况进行比较,如图13所示。正如预期的那样,当公共电压穿过分裂平面时,公共返回电流的行为就像穿过分裂的单端走线,类似于我们在图8中看到的情况。唯一的区别是没有100%的共同电流,所以我们也看到了一些不同的返回电流。

图13当引入差分26.3 ps对内偏斜时(左)与无偏斜情况(右)相比,差分返回电流在参考平面上的表现示例。

最后,要解决的最后一个论点是,如果有一个相邻的地平面,在它和分路电源平面之间有一个非常薄的电介质,它将作为一个更好的穿过分路的返回路径。从信号完整性的角度来看,逻辑上这是有意义的,因为走线的阻抗将与穿过分路的走线和参考平面之间的介电厚度成比例地减小。

在前面的例子中,我们假设一个0.062英寸厚的4层板。这在很大程度上决定了叠层内部核心介电层的厚度。为了使参考平面穿过间隙更靠近电源平面,PCB层数需要增加到最少6层,以保持对称堆叠和0.062英寸厚度。

如果我们减小间隙下的介电介质厚度,重新模拟5mil间隙场景,我们可以看到图14所示的单端驱动一条走线的结果。选择2密耳的薄电介质;表示通常用于功率平面去耦的埋地电容铁芯层压板的通用厚度。再加上如图1所示的5 mil厚度H1和1.2 mil厚度的电源平面L2,我们得到间隙下的总介电厚度为8.2 mil。

在左边,我们观察到大部分回流电流在参考平面L2上的间隙周围被转移。在右边,当信号穿过间隙时,我们可以看到参考平面L3上的走线下的大部分返回电流。但是仍然有一些电流在L2参考平面上的间隙周围转移,因此仍然会辐射一些噪声。

图14间隙下介电厚度减小时SE返回电流密度在参考平面上的表现示例。在左边,大部分回流电流在L2的间隙周围转移。在右边,当信号穿过间隙时,大部分返回电流从L3的走线下流过。但是仍然有一些电流在L2参考平面的间隙周围改变了方向。

从信号完整性的角度来看,反射和NEXT的数量几乎减少了一半,如图15所示。传输信号的上升时退化较小,ext也得到了改善。

图15 5 mil间隙下SE入射/透射电压、NEXT/ ext比较厚电介质(H2=45密尔,蓝色图),薄电介质(H2=2密尔,红色图)与无间隙(黑色图)相比。正如预期的那样,L3的距离更近,可以减少入射反射和NEXT,同时最大限度地减少传输信号和ext的上升时间退化。

总结与结语

回到最初的辩论,谁是对的?结果是两边都有点对。本文探讨了微带几何中信号穿过分裂平面的几种情形。从信号完整性的角度来看,在某些警告下,微带走线穿过分裂平面可能是ok的。对于本研究中模拟的例子,只要将劈裂面之间的间隙减小到5mil,并且在相邻的电源接地层中使用非常薄的介电介质,串扰就不会明显增加。根据你的噪音预算,你可能会侥幸逃脱。

但在通过EMC方面,仍然存在更多的风险和疑虑。从来没有一种情况是,一部分返回电流永远不会沿着参考平面的分裂边缘流动,因此仍然存在EMI的风险。因为实际的设计有许多影响最终性能的相互依赖关系,所以很难提出一个通用的规则,说如果你这样做,并最小化你在每种情况下都可以。

作为微带拓扑的一般规则,似乎最好的做法是仍然远离交叉分割平面。当你不能做一个更详细的分析,应根据实际布局和堆叠板;或者寻找其他可以减轻噪音辐射的替代方案;比如增加额外的外部屏蔽。

最后,这就是我一直喜欢说的工程。”你不知道你不知道的事情会毁了你的一天。“本文试图强调的是,在当今的高速设计中,我们不能再仅仅局限于信号完整性、功率完整性或EMC。我们必须考虑所有这三个学科,并对它们进行教育,或者至少对它们有所了解。如果我们只关心信号完整性,而不了解EMC,我们可能会得出错误的结论,并且最终产品很可能无法通过EMC合规性测试。

参考文献

- 是德科技高级设计系统(ADS)[计算机软件],(2016版:http://www.keysight.com/en/pc-1297113/advanced-design-system-ads?nid=-34346.0&cc=CA&lc=eng

- PCI Express®外部布线规范,修订版1.0,2007年1月4日