使用二维场求解器准确预测特性阻抗

任何高速电路板堆叠设计的第一个目标是设计具有目标阻抗的互连,而该过程的第一步是使用二维场求解器来探索具有虚拟原型的设计空间。场求解器能多好地预测实际电路板上走线的阻抗?

对于科罗拉多大学博尔德分校的各种项目,我们构建了来自不同供应商的电路板,并发现根据提供的尺寸和Dk值,测量的走线阻抗与我们预期的不同。在少数情况下,差异超过15%。对于一些我们想用来说明信号完整性原理的测试工具,我们需要更精确地设计特定的阻抗轨迹。这一要求促使了这项研究。

我们的计划是使用二维场求解器来准确预测电路板上制造走线的阻抗。然而,要做到这一点,我们需要层的介电常数Dk的精确值。使用板上测试结构提取制造板的Dk,我们发现我们通常可以在目标值的3%以内实现痕量阻抗。我们是这样做的。

测试车辆

在这个实验中,我们使用极地仪器SI9000工具作为二维现场求解器。第一步是评估该工具与其他2D工具的相对精度。(这是在[1]中完成的。)对于相同几何形状的差分对传输线,所有商用工具的模拟阻抗都在1%以内。

但在实践中,二维场求解器的预测结果与电路板上走线阻抗的匹配程度如何?

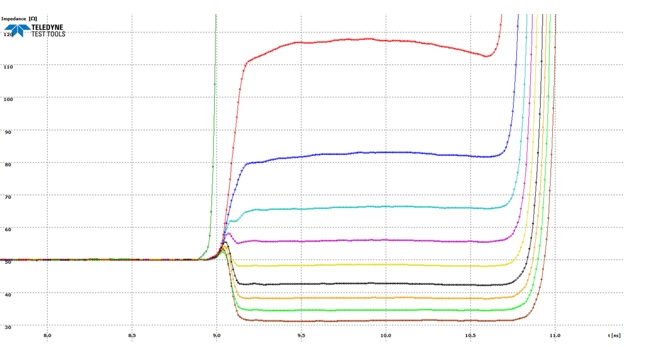

为了快速探索这个问题,我们使用了LPKF铣床在59mil厚的覆铜电路板上磨出各种宽度的均匀传输线,包括外层铜层(见图1)。每条线长6英寸。底层(不可见)是一个实心的连续地平面。

- 介质厚度

- 铜的厚度

- 线宽

- 介电常数

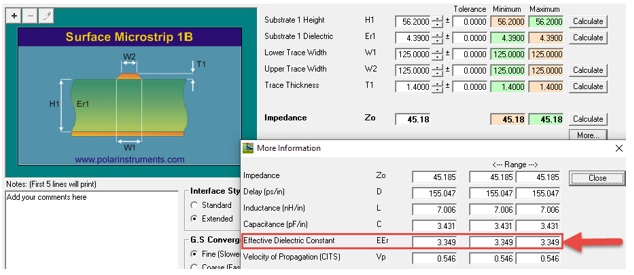

测得介质厚度为56.2 mils±0.5 mils。两个表面的铜厚度为1盎司铜,假设厚度为1.4密耳。用光学显微镜测量线宽,绝对精度在3%以内。我们需要输入二维场求解器的最后一个剩余项是电路板的介电常数。当被问及时,电路板供应商说它是4.2,他们提供的只是一个值,不知道频率。但它真的是Dk = 4.2吗?

测量Dk

供应商通常提供每层尺寸的堆叠图。有时它们不提供每层Dk的值,或者更糟的是,有时它们提供了一个值,但结果是错误的。

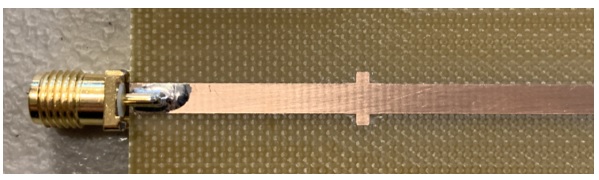

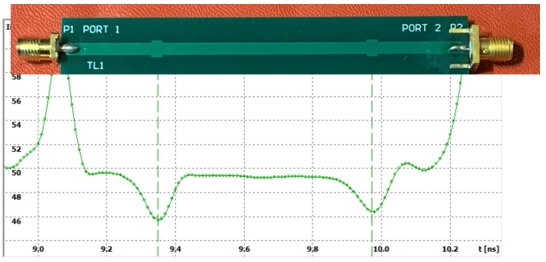

在之前的研究中,我们开发了一个简单的测试模式,将其放置在我们所有的电路板上,以测量特定层压板层的Dk。这是一条均匀的传输线,有两个相距精确距离的小不连续点。

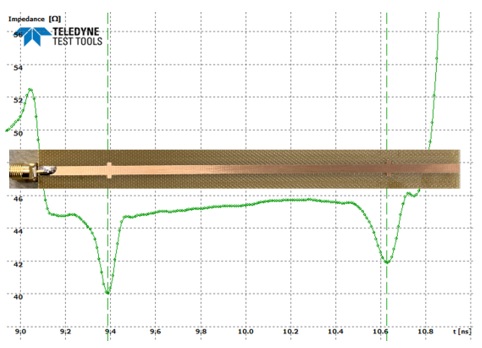

在走线的TDR测量中,两个不连续点之间的往返时间延迟被测量到10秒内。根据时延和长度,计算出信号的速度,并由此计算出有效Dk。图3显示了引起第一次反射的小衬垫的特写。

W1 = W2 = 125密耳

T1 = 1.4 mils

比较“设计”和“测量”阻抗

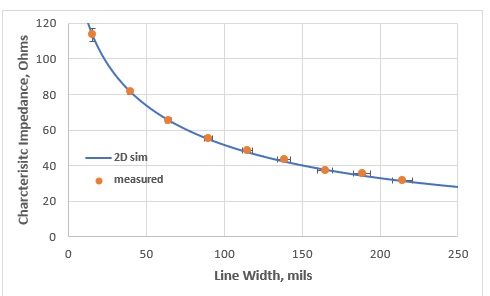

在给定尺寸和测量的体积Dk为4.39的情况下,将电路板上每条线的测量阻抗与每条线的计算值进行比较。图6显示了这种比较。

在这个范围内,最坏情况的差值为2.9%。这是线宽尺寸内的绝对精度。

该板的基本不确定度为线宽,受光学测量系统的限制。一旦测量了Dk,就有可能预测制备线的特性阻抗优于3%。

当我们看到测量值与模拟值在测量精度范围内匹配时,它总是一个重要的信心建立者。这并不意味着模拟是正确的,它只是意味着测量结果和2D现场求解器的预测是一致的。

这个简单的实验表明,在良好的输入信息下,二维场求解器可以准确地预测性能。

设计目标阻抗

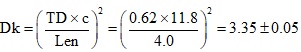

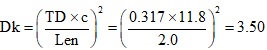

图7是一个测试线的例子,其中有两个小的不连续点,间隔正好为2.0英寸,以及它的TDR剖面。测量到的反射之间的往返延迟为0.635±0.01 nsec。有效Dk为

使用与之前相同的流程,我们为该板退出的bulk Dk为4.63。这假定在顶部表面有1密耳厚的焊罩。由于导体较宽,其冲击仅使阻抗降低0.6%,而使Dk值增加1%。

厂商指定的内核Dk为3.96。这与我们的测量值相差了17%以上。因为我们已经通过该供应商的商店运行了以前的电路板,我们知道散装Dk是什么,并使用我们的测量值而不是供应商的值来设计我们的测试线。

利用体积Dk为4.63,层的介电厚度和二维场求解器,我们可以设计线宽以实现50欧姆的目标阻抗。该制作的走线的测量阻抗可见为49.5欧姆,在目标值的1%以内。使用这种方法,我们可以使用二维场求解器设计任何我们需要的阻抗值。

结论

使用精确的二维场求解器、具有稳定工艺的晶圆厂供应商以及每块板上的特殊测试走线来测量和跟踪每层的总体介电常数,可以设计出目标阻抗在设计阻抗1%以内的制造电路板走线。

对于常规的高速应用,不需要这种精度水平。但是,对于演示特定信号完整性原理的特殊测试板,该技术对于创建可预测的互连结构非常重要。

当介电层较薄,线宽较窄时,焊掩膜的影响作用略大。在这种情况下,制造带有没有焊罩的测试痕迹的电路板将使提取的Dk具有更好的精度。

虽然该方法在本例中应用于简单的2层板,但它也可以扩展到多层板,其中应测量每层的Dk以获得所需的目标阻抗。

参考文献

Narula, Gaurav和Eric Bogatin。传输线分析的现场求解器:它们有多相似?印刷电路设计与Fab在线杂志-传输线分析的现场求解器:它们有多相似?,www.pcdandf.com/pcdesign/index.php/editorial/menu features/10472 -模拟- 1512.

Bogatin,埃里克。“用DMM测试TDR。”信号完整性期刊,信号完整性学报,2019年6月10日;www.lambexpress.com/blogs/8-for-good-measure/post/1282-test-your-tdr-with-a-dmm.