电源噪声可能会在FPGA核心逻辑[1]中造成定时故障,并可能增加输入/输出(I/O)块[2]的抖动。现有的电源完整性分析工具使用提取的配电网(PDN)在模具、封装和PCB上的s参数模型来评估有源电路[3]所看到的电源噪声。这些工具在定制集成电路设计过程中工作良好,设计人员可以完全访问模具、封装和PCB的原理图和布局设计文件。然而,在FPGA系统设计过程中,无法访问FPGA芯片和FPGA封装[4]的原理图和布局设计文件,限制了电源完整性分析的效率,增加了电源噪声引起故障的几率。在[5]中,Xilinx和Keysight的作者使用Xilinx 7系列FPGA器件包的s参数模型和印刷电路板的s参数模型,在Keysight ADS软件工具中创建了一个测试台架仿真。

本文提出了一种FPGA系统电源完整性分析的新方法,该方法将FPGA配置为自身配电网络(PDN)的矢量网络分析仪(VNA)测试仪器。该嵌入式VNA通过FPGA结构的逻辑电路测量PDN的阻抗频率分布,并提取出FPGA系统配电网络的完整s参数模型,其中包括FPGA芯片、FPGA封装和PCB上的PDN元件。然后,s参数模型可用于电路仿真工具,以评估FPGA核心逻辑中的电源噪声和FPGA I/O数据链路中的时序抖动。

实现

有两种基本类型的网络分析仪:仅测量幅度的标量网络分析仪(SNA)和同时测量幅度和相位的矢量网络分析仪(VNA)。s参数模型同时包含幅度和相位信息,因此,为了提取FPGA PDN的s参数模型,嵌入式测试仪器必须是VNA型。

商用试验台VNAs设计用于通过同轴电缆和连接器在受控特性阻抗传输线环境中与被测网络进行接口。传输线环境使测量各端口的透射波和反射波更加方便。FPGA嵌入式VNA具有与测量网络的接口,其中核心逻辑或I/O块连接到其芯片上的电源轨道。静态模式下,逻辑核和I/O块是连接在电源轨道上的高阻抗元件。这种功能模式可以将VNA端口设置为“开路”模式,因此对于芯片上的PDN VNA,更方便地测量z参数矩阵,然后将其转换为s参数矩阵。“开放”模式的寄生效应被包括在PDN模型中。

图1显示了FPGA实现的多端口VNA仪器的顶层框图。在该图中,VNA有一个测量端口连接到核心逻辑电源域VNA P1,其他测量端口连接到每个I/O组VNA P2、VNA P3……VNA P8。所有测量端口都由频率发生器和数据处理块控制,数据处理块通过计算机上运行的软件应用程序的串行数据链路控制。

图1 - FPGA嵌入式矢量网络分析仪(VNA)的顶层框图

激活端口n产生正弦电流 通过PDN。其他端口为高阻抗“open”模式。这种正弦电流在端口处产生正弦电压变化

通过PDN。其他端口为高阻抗“open”模式。这种正弦电流在端口处产生正弦电压变化 以及正弦电压变化

以及正弦电压变化 如果在PDN中存在耦合,则在其他端口。所有VNA端口都测量其相应功率域电压变化的幅度和相位。

如果在PDN中存在耦合,则在其他端口。所有VNA端口都测量其相应功率域电压变化的幅度和相位。 参数通过除法计算

参数通过除法计算

VNA端口结构

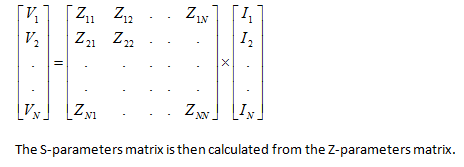

本设计中的每个VNA测量端口包括发射机和接收机,如图2所示。

图2 - VNA测量接口框图

变送器通过顺序激活和取消激活可变数量的恒流负载块(a),通过配电网络产生正弦电流。每个恒流块由FPGA逻辑块或FPGA I/O块组成,通过对多个瞬态开关电流进行排序,使它们叠加到从正供电轨拉出并推入负供电轨的整体恒流。恒流负载的激活由正弦定序器(b)控制。正弦电流的频率由FPGA中配置的可编程频率发生器控制。

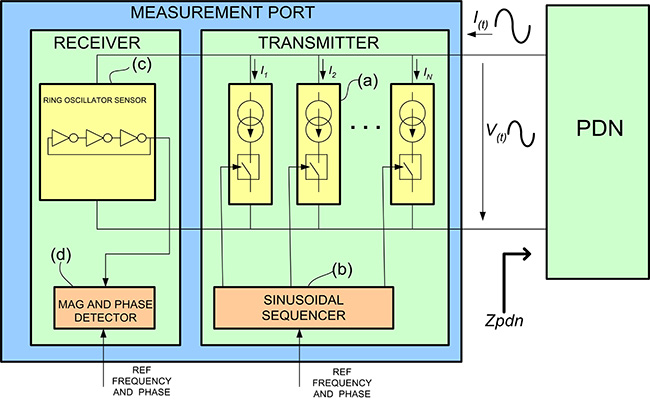

来自发射机的正弦电流,我(t)产生正弦电压变化,V (t),在电源域上按公式计算V (t)=我(t)*Zpdn,在那里Zpdn是配电网的阻抗。图3显示了VNA发射机端口产生的FPGA电源电压的正弦变化示例。

图3 - VNA发射机产生并在板上测量的FPGA核心逻辑电压供应的正弦变化

上面的道线表示在板上测量的FPGA电源电压,下面的道线表示在VNA发射机端口产生的触发信号。

接收机包括一个环形振荡器(c),其功率域与发射机相同。这个环形振荡器看到正弦电压变化V (t)作为调幅电源。环形振子的振荡频率与环形振子链的每一级的延迟成正比。每个阶段的延迟在电源电压降低时增大,在电源电压升高时减小。因此,电源电压的正弦变化,V (t),对环形振荡器的频率进行调制,如图4所示。

图4 -由电源电压变化引起的环形振荡器调频

当电源电压恒定时,环形振荡器以恒定的频率振荡,如图(a)所示。当正弦电源电流负载为有源时,电源电压变化如图(b)所示,环形振荡器的频率按照正弦变化进行调制,如图(c)所示。

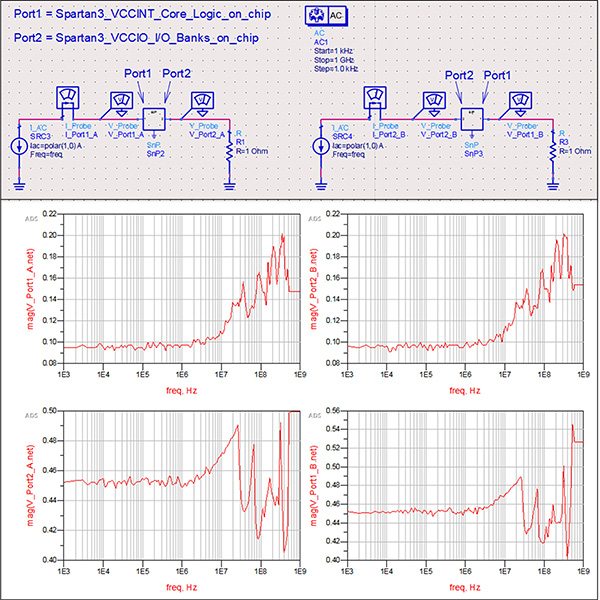

图2中的幅度和相位检波器块(d)测量环形振荡器的调制幅度和相位。阻抗参数的大小计算为

在Z神经网络表示配电网口的阻抗参数n当端口n传输和所有其他端口都是“开放的”,f1被测频率与正弦电源电流负载是否有源,f2在正弦电源电流负载有功时测量的频率,V供应为配电网供电电压的标称值,我F0是否将可编程逻辑器件的电流消耗与频率正弦电源的电流负载设为零,以及我0是可编程逻辑器件的电流消耗与正弦电源电流负载不有源。相位由相位检波器测量,检波器以发射正弦信号的相位作为参考。当另一个VNA端口产生正弦电流时,测量的阻抗为Z锰参数,米为测量端口,n为发射端口。

然后将z参数矩阵转换为s参数矩阵。s参数依赖于源阻抗和负载阻抗,因此转换是对任意参考阻抗进行的Z裁判.这种转换使用了从电路分析的基本定律推导出来的代数计算。下面是一个将两个端口z参数矩阵转换为s参数矩阵的示例:

对于PDN模型Z裁判值通常为0.1欧姆,但也可以使用其他值。然后使用Touchstone格式在s参数模型中记录s参数矩阵。

测试板上的测量

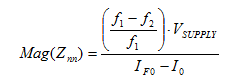

图5显示了在Spartan 3 FPGA测试板上使用双端口VNA IP测量的s参数模型示例。端口1测量VCCINT核心电源,端口2测量一个I/O组,VCCIO,电源:

图5 - Xilinx Spartan 3 FPGA在测试车板上测量的s参数模型

图5中的示例显示了s参数模型的开始和结束。最低频率为0hz,最高频率为587 MHz。为了将测量频率一直提高到FPGA的最大时钟频率,在本例中为587MHz,发射机正弦电流逐渐“失真”,在587MHz处为方波。从z参数矩阵获得s参数模型的一个优点是0 Hz值是直接从测量中获得的,而不是像发射/反射波测量那样从更高频率的测量中推断出来。

该s参数模型可进一步用于电路模拟器CAD工具,用于连接到FPGA的串行数据链路上的功率完整性和信号完整性仿真。图6显示了上述s参数模型在简单Keysight ADS电路仿真试验台中的示例:

图6 -使用Xilinx Spartan 3 PDN提取s参数模型的简单电路仿真

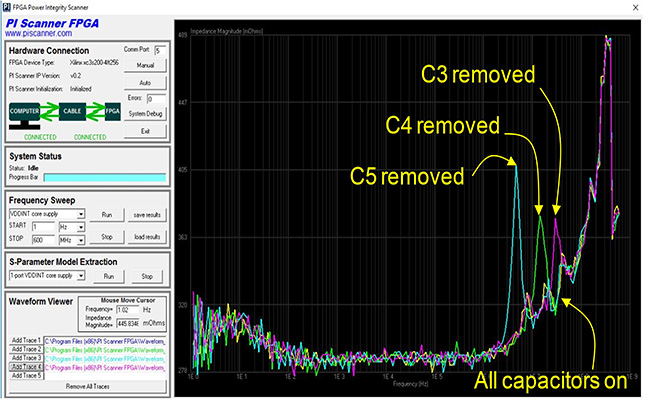

PDN阻抗幅值可以直接在测量应用软件中显示,如图7中使用VNA IP和PI Scanner工具的示例http://www.piscanner.com:

图7 -使用嵌入式VNA和PI Scanner软件应用程序测量FPGA PDN阻抗

该测量使用Xilinx Spartan 3 FPGA在测试板上完成,如图8所示。

图8 - Xilinx Spartan 3 FPGA测试车载板上核心逻辑电源去耦电容器的位置

解耦电容C3 (10nF), C4 (100nF)和C5 (10uF)已一次移除一个,并重新测量PDN阻抗。

优势

- 探测端口恰好位于FPGA芯片内部的逻辑门电源轨道上,因此测量结果准确地反映了FPGA结构电路在查看配电网络(PDN)时所看到的阻抗。

- 测量涵盖了整个系统级PDN,从FPGA芯片,通过封装,印刷电路板(PCB),一直到电压调节模块(VRM),包括VRM

- 测量包括在一些fpga中实现的模上电压调节器的阻抗和传递函数

- 该方法可用于3D-IC、堆叠芯片和多芯片FPGA,测量范围包括硅插入体和其他堆叠硅互连(SSI)上的PDN路径以及不同FPGA功率域之间的噪声耦合

未来的工作

- 在Xilinx Virtex UltraScale+或Altera/Intel Stratix10等大型高性能FPGA上测试该方法。

- 提出了一种从测量的整体模具+封装+PCB模型中去嵌入FPGA模具+封装s参数模型的方法。该模型可进一步用于新项目中PCB制造前的电源完整性和信号完整性仿真。

参考文献

[1]李慧,孙世双,王文安;博伊尔,p;Chee Seong Fong,“PDN在FPGA中可能产生时序故障”,2010年国际电磁应用会议和学生创新竞赛奖(AEM2C), pp 75 - 79

[2]李w.l., chin m.s.s, w.s.s choo, C.K. Chee Intel公司,“FPGA DDR同时开关输出抖动的预测方法”,第37届国际电子制造技术会议,马来西亚槟城,2016

Raymond Y. Chen, Sam Chitwood,“配电系统建模的s参数参数建模基础”,IBIS峰会,2005年6月14日,加州阿纳海姆

[4]金宗敏,李仁宇,金成俊,金素英,罗万洙,“基于去嵌入技术的未知芯片PDN提取方法”,韩国电磁工程与科学研究所学报,2013年6月,pp 633 ~ 643

安捷伦科技公司的Hany Fahmy和Colin Warwick以及Xilinx公司的Jack Carrel、Ray Anderson、Harry Fu和Romi Mayder,“使用s参数模型模拟FPGA电源完整性”,Xilinx白皮书WP (v1.0), 2012年1月