物联网(IoT)已成为将所有设备连接到互联网的新流行语。据《福布斯》报道,IHS Markit集团估计,2015年物联网设备的安装基数为150亿台,预计年复合增长率为15%。其他人估计的复合年增长率高达35%。到2020年,可能会有多达500亿个物联网设备。

虽然物联网包括从汽车和建筑到手表和心脏起搏器的所有东西,但本设计指南侧重于具有小尺寸和低能耗的物联网设备的低端。尽管这类产品与服务器主板的性能等级不同,但在设计周期开始时不注意信号和电源完整性设计原则,可能需要多个板旋转才能使您的物联网产品工作。

在本设计指南中,我们专注于以下方面的最佳设计实践:

- 两层板

- 带有射频组件

- 具有微控制器等数字器件

- 使用模数转换器(ADC)

- 低成本设计

- 专为低能耗设计

如果我们在设计中不做任何特别的事情,但假设互连是透明的,并且只是为连接而设计,那么产品仍然可以工作。毕竟,许多产品都是基于这种方法发布的。

如果没有对预期问题的严重性进行数值分析,我们永远无法100%确定产品将在第一时间发挥作用。但通过遵循这些最佳设计实践,我们可以降低风险,并增加设计成功的运气。当最佳设计实践是免费的,并且不增加制造或BOM成本时,它们应该成为“风险降低”过程的一部分。

使用经验法则、近似值和数值模拟的权衡分析是在产品构建之前执行成本-性能-风险权衡的最有效方法,并提供了更高的第一篇文章成功的机会。

作为一种设计策略,我们总是可以“买保险”,花更多的钱来过度设计产品,以增加性能边际。这进一步降低了风险,让我们有更好的机会在第一次就成功。成本降低可以在产品发布后进行。

我们在建立最佳设计实践以降低风险时使用的一般过程是识别可能出现的潜在问题,并设计实践以降低其严重性。

这里有十个推荐的最佳设计实践,以及一些正确和错误的例子。

为良好的信号完整性而设计

使用具有尽可能长的边缘过渡时间的器件,与所需的定时性能一致。通常情况下,您无法控制该功能,但请寻找它。至少,要知道所有信号的上升时间。

板的底层应是连续的接地面。如果你要分割地平面,你必须有一个强有力的令人信服的理由,而不是别人告诉你的。在99.9%的情况下,分割地平面会导致比修复更多的问题。

如果你确实需要在地平面下面添加一个十字,使它尽可能短,不要在分裂上路由信号。

即使你不需要它,也要把信号线布线成可控阻抗传输线。这意味着在信号线下面使用连续的地平面。千万不要越过回程路上的缝隙(参见防止地面反弹的章节)。

使用尽可能窄的线,你的晶圆厂供应商可以做到没有成本溢价。这意味着特性阻抗将高于50欧姆。这将降低充放电互连的功耗。如果互连密度较低,将信号线路由得尽可能远,以尽量减少串扰。只有在需要的时候,路线才会靠近。(见相声部分)

如果互连线比nsec中的上升时间短(以英寸为单位),则可能不必终止线路。例如,如果上升时间为3 nsec,则3英寸或更短的迹线可能不需要终止。当有疑问时,做一个简单的仿真建模,将互连作为均匀的传输线。但是,你需要知道驱动程序的输出阻抗。如果你不知道,假设最坏的情况下他们是10欧姆输出阻抗。要特别注意时钟的边缘,因为大多数设备都有边缘。至少模拟时钟网总是一个好策略。

如果跟踪足够长以至于需要终止,则在可能的情况下使用源系列终止。这将是最低的功耗。如果你追求最低功耗,就不要考虑远端终止。

信号的最佳路由拓扑是点到点。尽可能使用点对点的方法。另一种方法是使用雏菊链,尽可能短的存根到每个接收器。即使您必须使信号线弯曲,也可以使用菊花链来避免任何分支拓扑。当有疑问时,做一个简单的SPICE模拟,看看反射的大小。如果不需要较短的上升或下降时间,则在源处使用小串RC滤波器来增加上升或下降时间,以减少反射的影响,并减少进入信号线的电流。

为低串扰设计

即使所有的信号线都被设计成可控阻抗线,也会有线与线之间的串扰。它将表现为近端相声和远端相声。如果线路为50欧姆,且间距与线宽相同,则相邻线路之间会有5%左右的近端串扰。如果线路阻抗高达100欧姆,且间距等于线宽,则近端串扰可增加20%之多。对于高阻抗线路,5%近端串扰的间距应为线宽的5倍。

远端串音只会在表面、微带出现痕迹。远端串扰随耦合长度而增大,与上升时间成反比。使用50欧姆线和与线宽相同的间距,来自相邻迹线的远端串扰将为0.7% x Length[in]/RT[nsec]。如果信号上升时间为1 nsec,耦合长度为2英寸,则FEXT将为1.4%。可能没什么好担心的,但还是把数字写进去吧。

如果您使用高于50欧姆的阻抗,请使用场求解器来计算线对线FEXT和总线中使用的最接近的可接受间距。

测试设计

应选择一些信号线用于示波器探测或电路内测试。以下是测试设计时需要考虑的四个因素:

- 不要加载信号线。保持测试点连接与信号线尽可能短的存根。

- 探头位置使用尽可能小的捕获垫。使用丝印来识别探针点。

- 当信号在信号线上传播时,并不是信号线上的每个点都是等效的。探头点的位置应尽可能靠近RX端。

- 探测信号线时,还需要选择一个相邻点作为探测的返回连接。查看探头尖端的足迹,并使用信号和返回连接之间的间距来匹配探头。如果返回路径是下面的平面,在返回垫中为该平面添加一个过线。

为使用范围探测而设计

使用作用域探测的目标是不加载信号线,并保持信号带宽达到作用域。探测系统和示波器带宽应至少为信号带宽的两倍。如果信号的上升时间为3 nsec,则其带宽约为100 MHz。示波器和探头的带宽至少应该是200兆赫兹。这意味着数字示波器的采样率应该至少为1个GSps。

瞄准镜探头不应负载线。这意味着要使用高阻抗探针。许多可在1倍或10倍,1 Meg欧姆输入阻抗或更高,带宽> 300 MHz。然而,它们通常具有高达15pf的输入电容,考虑到驱动器的强度,需要评估15pf的电容负载是否会影响线路上的信号。如果驱动引脚的输出阻抗是35欧姆,那么来自范围探头的上升时间衰减将约为35 x 15 psec = 0.5 nsec,可能不是问题。

或者,高带宽范围探头可以与450欧姆电阻串联50欧姆同轴电缆。示波器输入端应为50欧姆。电路的负载为500欧姆。如果您的驱动程序可以处理这种负载,那么这个探针可能是一个高带宽的替代方案。如果驱动器输出阻抗为35欧姆,则连接探针的线路上的电压为500/535 =实际值的93%。

探头尖端应尽量采用低电感尖端。不要使用长而弯曲的地夹导线。许多瞄准镜探头都带有短的接地接头。这将减少尖端的电感,而不会降低带宽,更重要的是,减少来自电路板周围杂散磁场的任何感应耦合。

图1,使用紧密空间接地连接的探针尖端附件示例。

减少地面反弹的设计

当信号的返回路径不是均匀的平面,并且返回电流在相同的窄导体路径上重叠时,就会出现地反弹。它通常出现在包和连接器中。对于包中的地面反弹,你几乎无能为力。

为了不增加封装中的地反弹,将封装中任何未使用的数字I/O引脚设置为输出LOW,并将这些I/O连接到Vss连接。只要注意微处理器可能在启动或自检期间将输出更改为HIGH的任何机会。

从包的Vss引脚的顶部表面,用尽可能短的引脚连接到地平面。

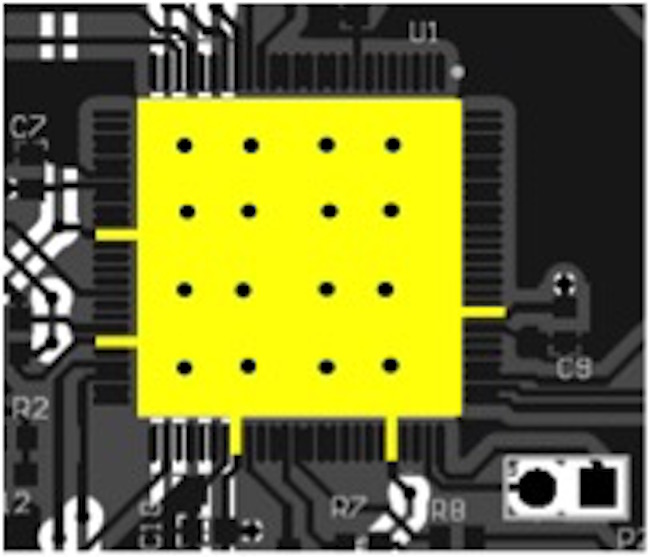

或者,如果封装下面的区域没有使用,就像外设引线封装一样,在封装占用区域下使用一个大的衬垫,在封装下面的接地平面上使用多个通孔,并将接地封装引脚向内布线到接地衬垫。在地面路径上使用尽可能短和宽的痕迹。

图2。封装下面的接地平面示例,通过通孔连接到下面的平面和封装Vss引线。

当使用连接器绕线或柔性电缆时,在信号线附近的电缆中交织接地引线。风险最低的是在电缆和连接器中交替使用G-S-G-S-G用于单端信号,G-S-S-G用于差分信号。更少的理由可能有效,但很难确定。

地面反弹的第二大来源是当信号在底层的地平面交叉分裂时。路由信号会在地面上的任何裂缝附近追踪。

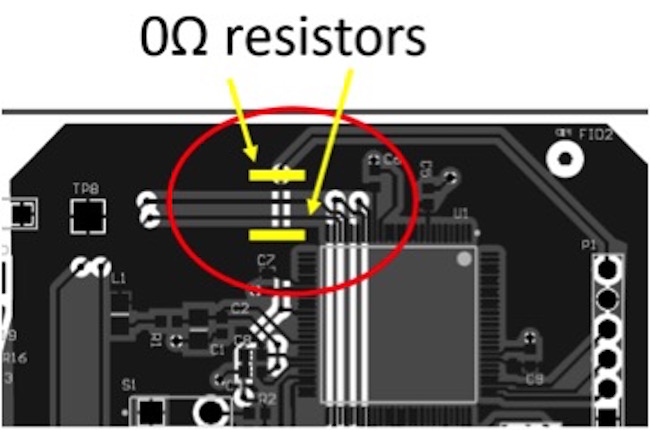

如果一个信号必须穿过一个地平面上的裂缝,在裂缝的两侧加一个通孔,将一个连接从地平面带到靠近信号线的顶层。在分叉两侧的通孔与相邻信号线的0欧姆电阻连接。使用尽可能短的连接在这0欧姆电阻路径作为实际。如果信号线的总线穿过一个分割,分离信号线足够的距离,路由每条信号线之间的0欧姆电阻,如果他们将适合。

图3。示例:两条信号线在一个平面下交叉一个分裂,相邻的0欧姆电阻提供一个连续返回连接。

低噪音配电设计

为了实现最低功耗,Vcc通常会尽可能低,并且通常会有一个电源管理IC (PMIC)和一个电源轨道。

一般情况下,设备的核心线和I/O线共用相同的电源轨和Vcc引脚。如果封装中有独立的芯线和I/O引脚,请保持它们分开,直到解耦电容安装到Vcc引脚上。这样它们就可以连接在同一个电源线路上。

任何电源引脚的目标是使用尽可能低的电感电容器安装在接近电源引脚作为实际。每个电容器将连接在Vcc引脚和Vss之间,或接地。两个连接(创建一个循环)都应该尽可能短。在电路板底部的Vss平面上放置一个通道,尽可能靠近电容器的Vss垫。

使用什么尺寸的电容器?在不了解当前要求的任何细节的情况下,选择您可以在电路板上组装的最小体尺寸的电容器,以及该体尺寸中最大的电容。每个Vcc引脚至少使用一个电容。如果更多的合适,每个电源引脚使用更多的电容器。

通常,PMIC和某种开关模式电源将用于重新生成正确的电源轨道电压。这意味着在驱动半桥的脉冲相关的动力轨道上可能会有一些周期性的波纹。这些信号通常被作为SMPS一部分的LC电路过滤掉。然而,电感器中有时会有较大的电流。这些可以作为近场磁场线耦合到板上的其他结构上。因此,最好使用环面来限制磁场,并使SMPS组件远离敏感信号线。

有时使用电阻分压器创建或检测其他电压,有时使用高阻抗电阻。高阻抗电路对交流电容拾取总是比较敏感。将高值电阻器放置在靠近感测引脚的位置,并在下方连续接地。

当传感线被用作SMPS输出的反馈时,将传感线路由为紧密耦合的微分微带,远离任何其他数字线。他们应该测量Vcc尽可能接近使用点。

如果你有一个对轨道电压噪声非常敏感且不吸收太多电流的设备,或者一个锁相环电源或ADC电源的设备上有一个特定的电源引脚,你可以在电源引脚连接上添加一个铁素体珠。一定要在铁氧体的设备侧加低电感电容。这是唯一的情况下,它可能是可接受的使用铁氧体在电力路径。

在Vcc引脚和电源管理IC (PMIC)之间路由尽可能宽的迹线。这意味着在底层连续地平面上,设计功率迹线的特性阻抗尽可能低。对于宽功率迹线,可以使用分支路由拓扑。更短和更宽的电源痕迹更好。

估计功率路径上的串联直流电阻。1盎司铜层的电阻约为0.5 mOhms/平方。计算功率迹线的平方数,以估计其串联电阻。如果电源痕迹是25密耳宽,1英寸长,将有1/0.025 = 40平方。总电阻为0.5 mOhms/平方x 40平方= 20 mOhms。如果电流为100 mA,则电压降为20 mOhms x 0.1 A = 2 mV。在您的应用程序中,电源轨上的电压降是否可以接受?通常导轨可以承受50-100毫伏的跌落。

避免在顶层使用铜填充,即使它是连接到地面的。相反,保持信号线之间的间隔,并使电源痕迹尽可能宽。功率走线越宽,串联电阻越低,路径上的电感越低。

低能耗设计

嵌入式应用中消耗的大部分能量都在微控制器核心上。第一步是使用尽可能低的核心电压,但当核心电源波动时,要有足够的余量来保持电压高于最小值。

在编写代码时,监视设备的实际功耗以查看哪些操作消耗的能量最低是很有用的。例如,典型的整数数学比浮点数学消耗更少的焦耳。

最终的能源将是电池或使用超级电容器进行局部存储的能量收集设备。这些将馈送电源管理IC (PMIC)以提供调节电压。PMIC应根据消耗的平均功率选择,并在稳压侧使用大的低电感电容器,以提供大电流突发。

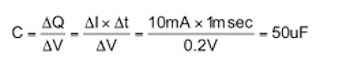

所需电容的大小可以根据允许的压降ΔV和电流浪涌的持续时间Dt以及电流浪涌的大小ΔI来估计。例如,如果将有10ma的电流浪涌持续1 msec,并且电压供应余量从稳压电压水平到磁芯所需的最小电压为0.2 V,则磁芯电源上的电容器尺寸应至少为:

分布在每个Vcc引脚上的电容器也将有助于维持电压水平并增加设计裕度。

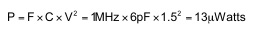

在电路板水平上,为降低能耗所能做的最好的事情是使用低电容的互连走线。FR4中的50欧姆线路约为3pf /英寸。如果它是2英寸长,它将是大约6pf的容性负载。如果一条控制线或数据线上有一个1.5 V的信号,它将在1 MHz时发生变化,由于一条线而耗散的功率是:

如果电路板上有60条线,则在电路板级互连的充放电过程中大约消耗1 mWatt的功率。

为了达到最低的能耗,尽可能使用短的互连,尽可能使用高阻抗。当你看到高特性阻抗线时,知道它们可能有更高的串扰,所以也要注意这一项。

稳定开启设计

当PMIC打开时,所有的分布式电容器都必须充电。一般情况下,在输出电流较低的PMIC中,涌流会使电源轨低,导致一些设备关闭,一些设备打开。

励磁涌流可以通过将功率迹线隔离到高电流牵引器件并使用串联MOSFET作为功率门来控制。与10 k电阻分流,这将作为一个缓慢的预充去耦电容器。例如,如果有100uf的电容,10k电阻将在大约2秒内为它们充电。在受控延迟后,预充电接近Vcc水平,MOSFET可以将剩余的Vcc功率按顺序门控到每个设备,以实现稳定和可预测的打开。

在ADC中设计低噪声

模数转换器(ADC)通常是电路板上对噪声最敏感的器件。它通常连接到电路板上的传感器或通过外部电线连接。将ADC放置在尽可能靠近传感器或电路板边缘的地方,以减少电路板上的迹线长度。在模拟线之间使用尽可能大的间距来减少串扰。

为了进一步减少串扰,使模拟线尽可能宽,与传感器的源阻抗和所需的时间响应一致。将模拟线与数字线物理地分开,并在下面设置连续的返回路径。

通常,封装有一个单独的模拟地和数字地引脚。这是为了防止从数字信号耦合到封装中的模拟信号的地反弹噪声。将两个接地连接到电路板上的同一接地面是可以的。

如果模拟端有一个单独的Vcc引脚,在这种情况下,使用铁氧体珠串联Vcc电源引脚是可以接受的。一定要把去耦电容放在铁氧体珠的设备侧。

设计为低耦合射频接收机

将所有RF组件放在电路板的一端,远离数字线和模拟线。在射频部分下面使用与电路板其他部分相同的连续地平面是可以的。

考虑将RF部分放置在单独的板上,使用电缆连接,在它们之间只使用电源、接地和数字控制线。在可能的情况下,将电源线和地线与数字信号线交织在一起,以减少接地反弹。

图4。一个远离数字控制电路的独立射频模块的例子。

如果它们由与其他组件相同的电源供电,请考虑在电源路径中使用铁氧体,尽可能靠近射频区域,并在射频设备的Vcc电源引脚附近使用局部去耦电容器。这是为了防止来自电源轨道的噪声进入射频设备的敏感接收器放大器。

虽然遵循这些最佳设计实践并不能100%保证产品能够正常工作,但这些步骤将降低破坏预期应用程序的噪音风险,并增加成功的机会。