信号和功率完整性(SI/PI)模拟、测量和分析通常存在于两个不同的世界,但偶尔这些世界会发生冲突。当我们提到特性阻抗时,就会发生这样的碰撞,Z0.传统上PI世界存在于频域,而SI世界存在于时域。

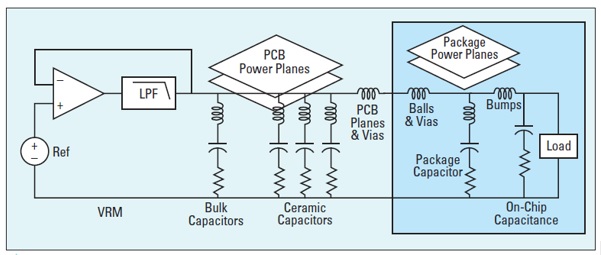

在PI世界中设计配电网络(PDN)时,我们最感兴趣的是设计一个低于目标阻抗的平坦阻抗,从直流到瞬态电流的最高频率成分。实际上,这是通过如图1所示连接到各自功率平面的具有不同值的电容器网络实现的。

图1典型PDN礼貌[1]的简化模型。

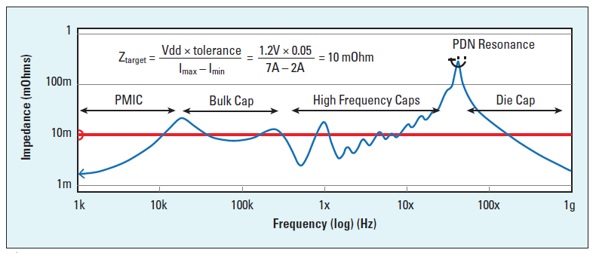

在现实世界中,没有理想的电容器这样的东西。总有寄生元件称为等效串联电感(ESL)和等效串联电阻(ESR)。PCB的物理特性,如组件安装电感,平面扩展电感,通径和BGA球电感,以及电压调节模块(VRM)特性也有助于阻抗剖面。当电容连接在一起时,寄生电感和电阻的相互作用产生了一个具有谐振峰值和抗谐振空值的传递阻抗曲线,如图2所示。

在频域以对数对数尺度计算并绘制了级联节点与负载之间的传输阻抗。然后将得到的阻抗曲线与目标阻抗(Z目标),根据允许噪声纹波和最大暂态电流估算。在分析中,平面目标阻抗与频率无关。

图2从模组电源导轨上的垫片上看PDN的阻抗剖面。

谐振峰是由于一个电容器的ESL与另一个电容器并联。抗谐振空值是由于每个电容器的ESR, ESL和C的串联组合。不同的电容值会在不同的频率下产生反谐振空值。

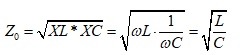

但在圆周率的世界里,有一个很少被提及的特性阻抗,Z0.在这种情况下,它是指一个电容器的无功阻抗(XC)和一个电感的无功阻抗(XL)的几何平均。

方程1

谐振时,XL和XC在特征阻抗处相交,并相等,如图3所示。

图3理想电感和电容的感容电抗随频率的变化图。在共振时,XL和XC相等,并在特征阻抗处相交,Z0.模拟Pathwave ADS[6]。

这是一个非常重要的观察结果,也是SI/PI世界碰撞的地方。

在SI领域,特性阻抗,Z0指沿无反射的均匀传输线行进的波阵面电压与电流的瞬时比值。对于一条无限长的均匀传输线,Z0等于输入阻抗。

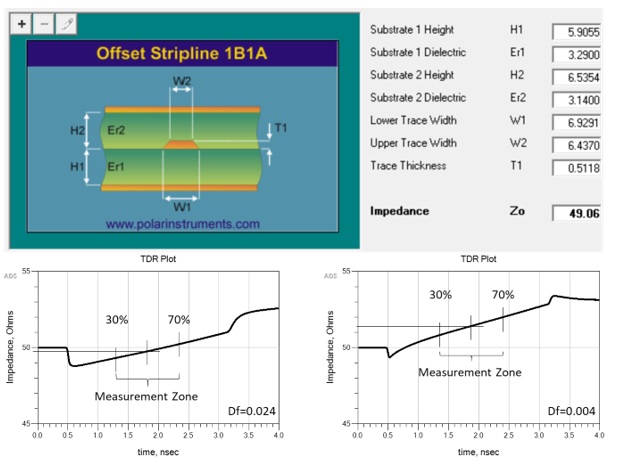

有损耗传输线的特性阻抗定义为:

方程2

其中R为单位长度的电阻;G为单位长度的电导;L为单位长度电感;C为单位长度的电容。对于无损均匀传输线,假设R和G为零,则特性阻抗减小为:

方程3

时域反射计

在SI领域,我们通常使用时域反射计(TDR)来测量特征阻抗,但通常情况下,我们得到的测量阻抗不是我们用2D场求解器预测的。大多数PCB FAB车间使用的许多2D场求解器仅在单个频率下计算横截面几何结构的无损特性阻抗,该频率由介电常数(Dk).它没有输入导体电阻率、介质损耗或导体的长度。

因此,问题是:我们设计了堆叠,然后根据堆叠参数和匹配的特征阻抗进行SI建模分析。但是PCB FAB车间经常会调整线宽(s),超过正常的工艺变化,以便在测量时,阻抗将落在指定的公差范围内,通常是+/- 10%。

部分问题在于测量的方法。大多数PCB工厂遵循IPC-TM-650测试方法手册[2]。但它有局限性,因为Z0测量是推导出来的,不能直接测量。原因是测量包括电阻和介电损耗,直到沿着TDR图进行测量为止。

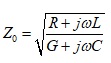

电阻损失通常导致阻抗曲线缓慢单调上升,如图4的示例TDR图所示。IPC-TM-650规定了30- 70%的测量区域,以避免探测感应环影响测量。大多数PCB FAB车间将测量这个范围内的平均阻抗,通常在中心区域。

根据线宽、厚度和介电损耗系数而定(Df)时,单调上升的斜率会发生变化。

图4示例TDR图,显示阻抗由于电阻损失和IPC-TM-650测量区而缓慢单调上升。

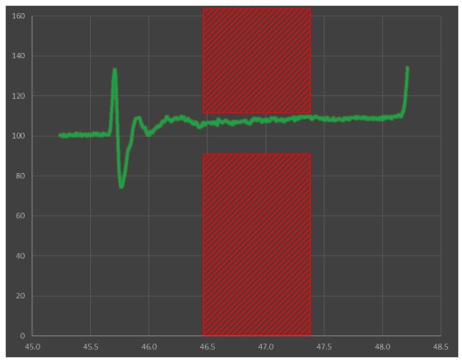

问题是IPC-TM-650测试方法上一次更新是在2004年,当时更高的介电损耗,以及更宽的线宽和更厚的铜重量被更经常地使用。一个更高的Df趋向于通过压平斜率来补偿电阻性损失,如图5所示。

左下角是使用高损耗电介质的模拟TDR图Df= 0.024。右边有完全相同的几何属性,除了Df= 0.004。在50%点测量时,平均阻抗左侧为49.8欧姆,右侧为51.4欧姆。同时,我们也确认了高损耗材料的坡度较平缓。

图5中Polar SI9000 2D场求解器[5]预测的实际特征阻抗为49欧姆。对于损耗较大的材料,在测量区域内进行测量不会有任何问题。但是对于低损耗材料,电阻性损耗占主导地位,在测量区域内测量将比高损耗材料给出高5%的阻抗读数。正确的测量点Z0实际上是初始倾角,相当于场解算器的预测。根据指定的公差,这可能会影响产量和成本。

图5 Polar SI9000二维场求解器[5]特征阻抗预测(上)。使用高损耗电介质(左下)与具有完全相同几何形状的低损耗电介质(右下)模拟2英寸TDR图。更高的Df补偿了更高的电阻损失,从而使曲线变平。模拟Pathwave ADS[6]。

今天,随着低损耗电介质和更细的线宽和更薄的铜重量的推动,使用TDR测量真正的传输线特性阻抗变得更具挑战性。在测量微分阻抗时更是如此,因为线宽空间几何形状的变化可以对测量的微分阻抗产生更深远的影响。

以新设计的第一篇文章构建为例,让我们假设在TDR图缓慢单调上升的开始测量的正确特性阻抗处于标称+ 10%公差的高端。假设是54欧姆。但是由于低损耗介质和高阻性损耗,中点的TDR测量读数现在在57欧姆时高出5%。这将意味着阻抗现在超出规格超过标称和板将被废弃。

然后PCB工厂将返回并相应地调整线宽,以使测量在测量设置的范围内。这样做有效地降低了真正的标称特性阻抗!

如果随后的制造变化将测量阻抗推向- 10%公差下限的测量区域内,例如44欧姆,那么如果在初始倾斜处测量,真实的特性阻抗将在42欧姆处降低5%,并且超出规格。但由于按照IPC-TM-650测试方法进行测量,因此该板将通过测试。

2端口分流测量

但如果还有别的办法呢?如果我们可以借用PI世界的阻抗测量技术来确定SI世界中真正的传输线特性阻抗呢?当然有。进入2端口分流测量技术。

例如,在PI领域,为了测量被测设备(DUT)的片式电容器的ESL和ESR,通常使用2端口分流测量。它很像用于测量极低直流电阻的4点开尔文测量技术。

2端口分流测量通常用2端口矢量网络分析仪(VNA)完成。VNA的端口1输出校准信号,端口2测量DUT的电压信号。在测量超低阻抗[3]时,通常还使用隔离变压器来断开固有的接地回路。

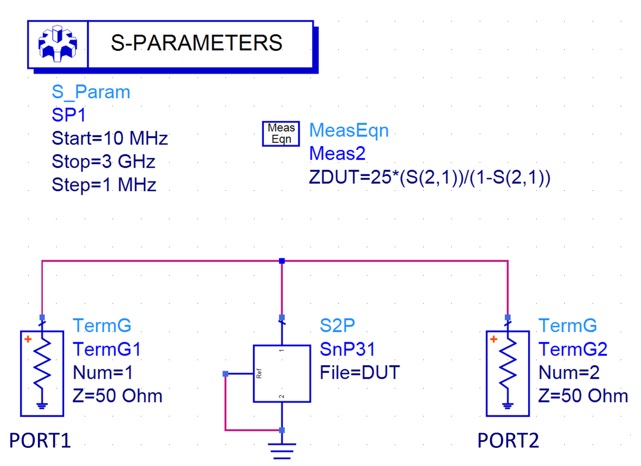

一旦测量完成并将s参数保存为试金石格式,就可以在您最喜欢的SPICE模拟器中进行进一步分析。图6是使用流行的Pathwave ADS[5]的通用原理图,可用于2端口分流分析。

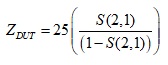

当DUT的端口1和端口2连接到DUT的端口1,并且DUT的端口2接地时,DUT的阻抗可由[3]确定;

方程4

图6通用Pathwave ADS[6]原理图,用于DUT的S2P文件上的2端口分流分析。

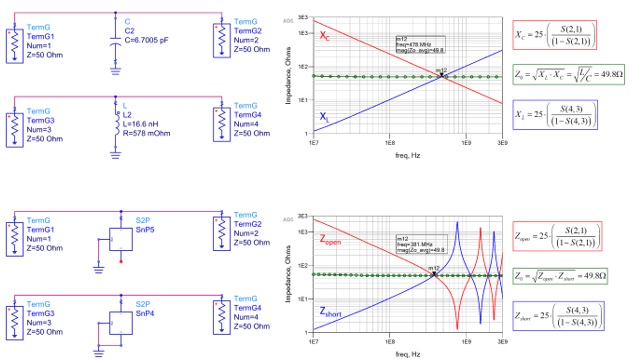

如果我们将图6中的DUT替换为电容和电感,我们将得到如图7所示的阻抗图。正如我们前面看到的,当我们用公式1取感应电抗和电容电抗的几何平均时,我们得到了特征阻抗。如果我们将公式4应用于电容和电感的2端口分流测量结果,我们得到与图7顶部所示完全相同的结果。

当我们用图5中的传输线模型的s参数文件替换电容和电感时,我们得到图7底部所示的图。除了谐振零点和峰值,在一定频率范围内,传输线的阻抗看起来像远端打开时的电容阻抗,远端短路时的电感阻抗。正因为如此,这是两个世界碰撞的地方!

如果我们取远端开放时阻抗的几何平均(Z开放)或短(Z短),得到该频率下的特性阻抗。我们注意到红色和蓝色阻抗线第一次相交的地方,正是该频率的几何平均特征阻抗。

同样值得注意的是,这些线相交于高频率的峰谷之间的频率的一半。

图7远端断开时(实心红色)与远端短路时(实心蓝色)的电感和容抗阻抗与频率的关系(上)和传输线阻抗与频率的关系(下)。红蓝线的交点就是特征阻抗。模拟Pathwave ADS[5]。