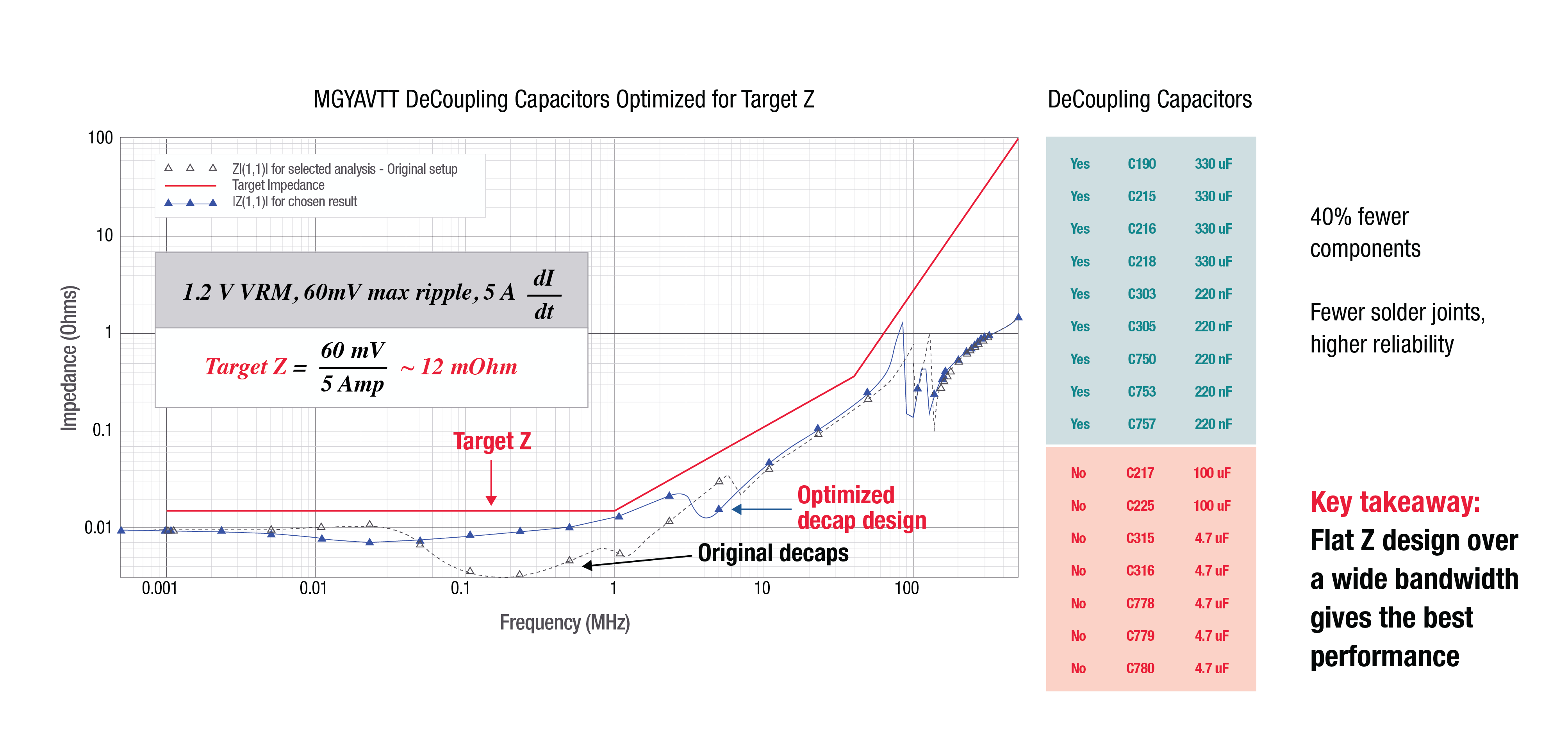

在高速数字设计中,只需要一个流氓电压波就可以杀死一个配电网络(PDN)。当来自多个PDN共振的波纹在相位上排列,产生过多的异常电压波[1]时,就会发生异常电压波。布局前的平面阻抗优化降低了设计中出现异常波的风险。功率完整性(PI)工程师使用目标阻抗来设计宽频率范围内的功率传输。目标阻抗是一个简单的估计值,使用最大允许纹波除以最大期望电流阶跃负载。例如,在现场可编程门阵列(FPGA)中,最大纹波为60 mV,最大电流步进负载为5 a,目标阻抗(Z)为12 mOhm(见图1)。

在较宽的频率范围内实现这一目标阻抗需要低频率的电源和高频率的去耦电容器。挑战在于以最低的成本获得最好的性能。平面阻抗设计使这成为可能。为平坦阻抗设计的PDN使用最小数量的电容器来实现目标阻抗,同时避免高Q谐振,这可能导致流氓电压波。减少零件数量有更高的可靠性和更少的焊点的额外好处。

图1:在这个FPGA示例中,60 mV纹波除以5 A得到的目标阻抗为12 mOhms。

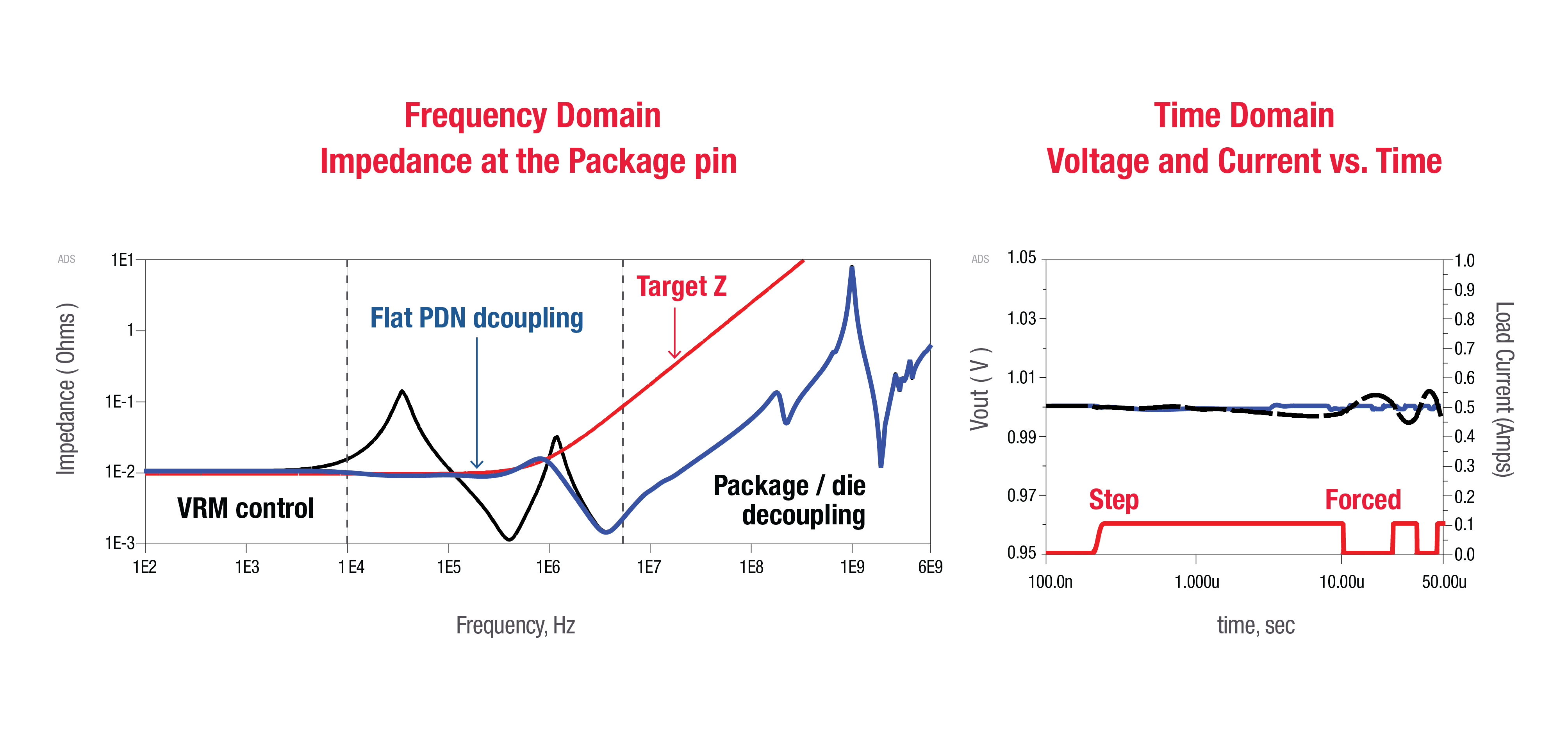

图1显示了目标阻抗掩码为红色[2]的1.2 V电源轨阻抗随频率的变化曲线。红色的Target Z显示了电源和印刷电路板(PCB) PDN必须向负载提供电源的平坦区域。第一个断点约为1 MHz,显示内部封装/芯片电容开始向负载提供电源的频率。第二个断点表明载荷的频谱含量随着频率的增加而迅速减少。当di/dt趋于零时,允许更高的PDN阻抗。

PI设计器只能控制电压调节模块(VRM)和PCB去耦电容器所覆盖的频率范围。这就是平面阻抗设计可以提高性能和降低成本的地方。

选择去耦电容器的挑战在于,在目标阻抗的mOhms下,PCB路由寄生和组件封装寄生是显著的。从数据表中利用的去耦电容器建议可能不再准确或提供最佳结果。选择错误的电容器会导致不必要的共振和潜在的异常波动。

异常浪是如何发生的

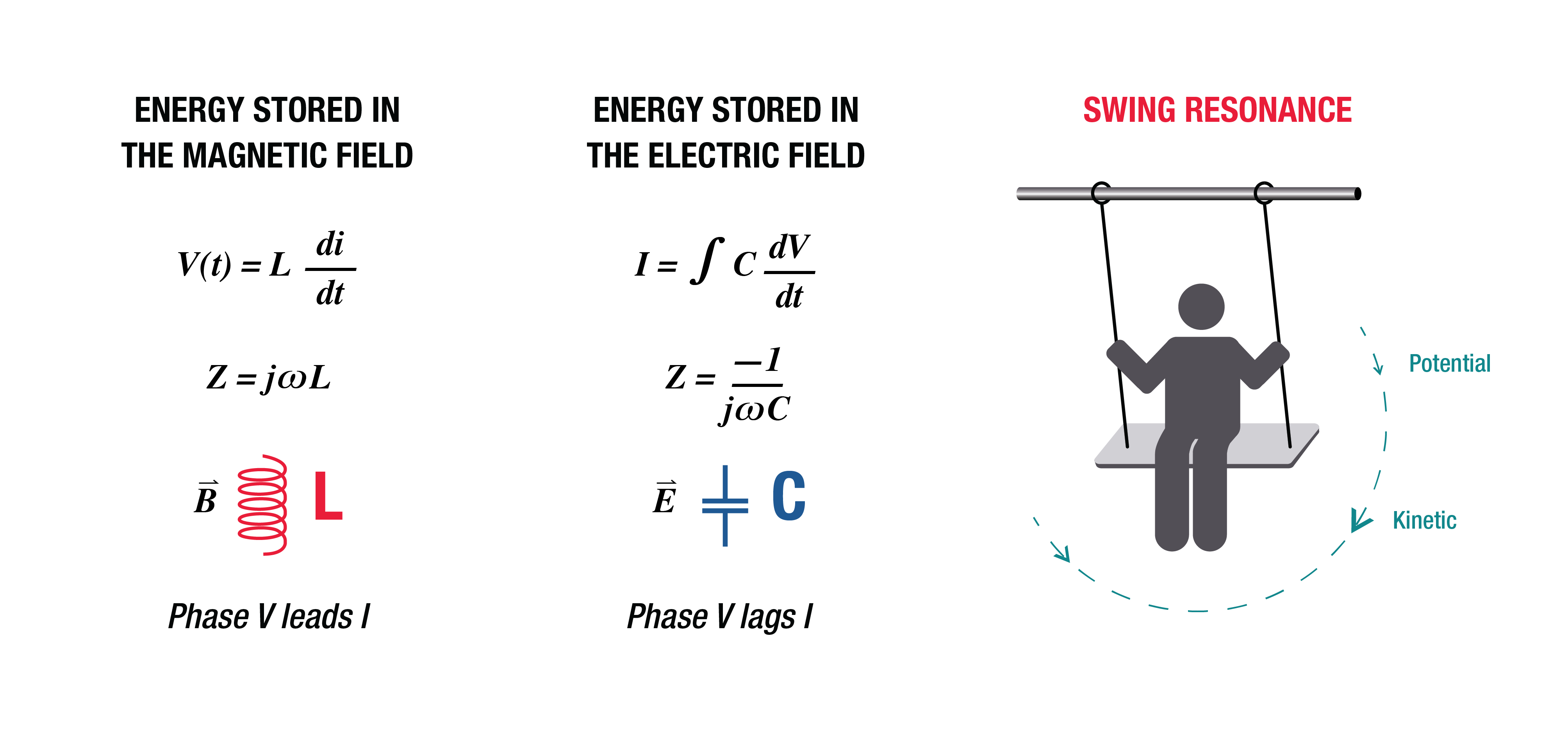

为了避免在电源轨道上产生导致异常涌浪的谐振,了解异常涌浪是如何发生的是很重要的(见图2)。电源轨道上常见的振铃来源是电感器(L)与电容(C)的平行谐振。电感器以电压引导电流的相位在磁场中存储能量。电容器在电场中储存能量,电压相位滞后于电流。就像能量在势能和动能之间振荡的秋千一样,电感器和电容器中的电流来回移动。

图2:电感和电容器的并联谐振导致电源轨上的振铃。

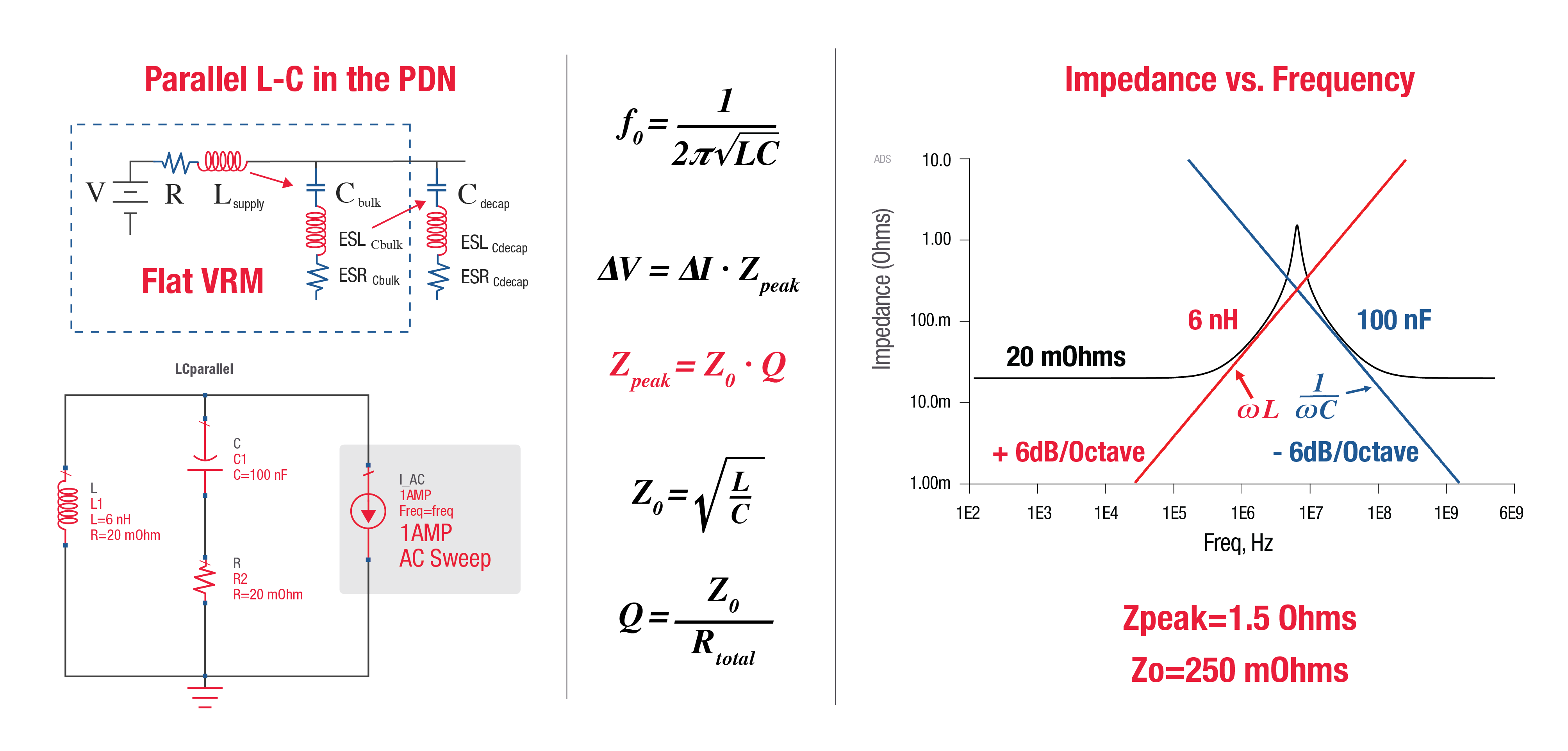

原理图(见图3)说明了电源轨上平行信用证振铃的根本原因。一个简单的串联R-L模型显示了VRM的有源电感是如何与大容量电容器并联的。散装电容器也有与较小的去耦电容器并联的内部串联封装电感。在左下角示意图的简单spice类型模拟中,1 a交流电流负载的扫描激发平行L和C以生成右侧的阻抗与频率图。

图3:与并联去耦电容谐振的电感模拟预测功率轨在1.5 Ω阻抗峰值频率上的振铃。

仿真结果清楚地显示了在LC谐振频率处的峰值阻抗。一些基本的电方程描述了峰值频率,并表明最大阻抗取决于共振的锐度或Q。随着L和C的串联增加实际电阻会降低q,这个串联电阻在设计平面阻抗时很重要。有助于降低谐振Q的电阻称为阻尼电阻或缓冲电阻。

图3右侧的阻抗图显示了VRM的20 mOhm电阻在低频时是如何占主导地位的。随着频率的增加,VRM的有源电感起作用,电感斜率上升6nH。然后,VRM电感与体积电容器的100nF向下斜率共振,以给出1.5Ω的峰值阻抗。该阻抗峰值表明PDN中的共振,当被该频率的强制函数激发时,会导致电压纹波比阶跃响应大Q倍。激励多个PDN谐振频率会导致超出设计边界的流氓电压波。

增加合适的平阻抗去耦电容器

为了理解如何选择正确的去耦电容器,请查看当VRM连接到封装/模具模型而没有去耦电容器时PDN的设计(参见图4)。左边的图表显示了负载与VRM系列R-L模型直接连接到封装/模具行为模型时的阻抗与频率。在本例中,封装模具仿真模型是来自供应商的s参数数据文件。

原来的系列R-L模型是虚线黑色痕迹。红色虚线是封装模具s参数模型。蓝色轨迹是将两个模型连接在一起时在负载处看到的阻抗。VRM的电阻行为是在低频。由于没有去耦电容器,只有封装/模具模型,VRM输出电感与封装电容并联产生高阻抗谐振。在较高频率下,封装/模具s参数模型的行为主导负载阻抗。

右边的对数时域图显示了阻抗峰值处的强制响应,在最坏情况下会导致功率轨上的电压纹波。峰值阻抗可能低到足以处理单步,但在此频率下的强制响应呈指数增长,显示出最坏情况下的噪声涟漪。消除共振需要增加去耦电容器。

.

图4:在没有去耦电容的情况下,VRM加负载的并联谐振会导致阻抗峰值。采用对数时间尺度的时域仿真结果表明,系统的强制响应波动过大。

增加一个系数为10的电容,例如从以前的设计或数据表推荐中利用的100uF电容,可以降低阻抗峰值(见图5)。在原始峰值阻抗频率处产生的时域纹波较小;然而,请注意,添加这个不正确的电容器已经创建了两个新的阻抗峰值,如蓝色轨迹所示。

散装100uF电容是平面阻抗的错误值,第一个峰值显示它与VRM电感共振。第二个较高的频率峰值是电容器的等效串联电感与封装/模电容谐振。这两个峰值较小,但可能仍然不能满足所需的目标阻抗,留下异常波的可能性。每个峰值需要额外的电容来获得所需的平坦目标阻抗[3]。

.

.

图5:选择错误的去耦电容器会导致更多的平行谐振阻抗峰值。

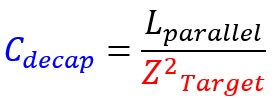

最终,增加足够的电容器驱动阻抗低于目标设计阻抗。然而,有一种更好的方法可以最大化性能并最小化成本。不是从数据表或以前的设计中利用建议的电容值,而是使用简单的L /目标Z平方方程来找到平坦阻抗[4]所需的C:

通过为平坦目标阻抗设计pdn, PI工程师可以选择正确的电容值并减少零件数量(见图6)。图6右侧的时域图显示,平坦阻抗(蓝色实线)比非平坦阻抗产生的纹波更少。这个简单的设计示例是一个很好的起点。然而,对于一个真实的系统,PCB和组件寄生是非常重要的。PI工程师需要一个完整的工作流程来设计和测试最终产品。

图6:平面阻抗PDN设计提供了最大的稳定性和最小的纹波(蓝色痕迹)。

通过完整的工作流程确保电源完整性

在完整的PI工作流中,设计人员从VRM、去耦电容器和负载[5]的良好模型开始。通常,最好的模型是基于测量的,例如VRM的状态空间平均模型或给定应用环境的电容的测量s参数模型(见图7)。接下来,设计人员执行预布局调查,以了解电源完整性挑战并提供布局指南。

一旦PCB布局完成,设计人员运行一个完整的布局后EM模拟,并使用结果来优化解耦电容器的位置和值。最终的布局后PI生态系统仿真将高保真VRM模型与PCB EM模型、优化解耦和封装/模具模型连接起来,以观察小信号交流阻抗和负载瞬态,以及大信号DC-DC转换器开关纹波。测量是电力完整性工作流程的最后一步。它验证了纹波在规范范围内,负载定时和振幅抖动是可接受的,并且设计符合EMI/EMC标准。

.

.

图7:PI工作流在布局之前开始,并利用基于测量的模型进行模拟,以避免设计周期后期的故障,并降低产品成本。

太多的设计人员利用以前的设计或数据表示例,直到测量才进行调试。这是一种冒险且昂贵的设计方式。一些工程师使用由电源供应商提供的免费工具,如LTspice,但无法模拟PCB和解耦元件的EM寄生。PCB行业专注于后布局,因为这通常是经理必须在设计上签字以验证它是否准备好制造的地方。从布局后的EM开始通常会导致一个糟糕的设计的优化。

更好的方法是从预布局开始,在进行布局和优化之前探索正确的设计空间。结合电力完整性和电力电子仿真工具,覆盖了从发电到负载交付的整个PI生态系统。这为设计师提供了一个完整的工作流程,以避免在设计周期后期出现故障。

参考文献

s·桑德勒,”目标阻抗限制和流氓波对PDN性能的评估信号完整性杂志,2018年3月19日。

[2] H. Barnes, J. Carrel和s . Sandler,“32 Gb/s SERDES收发器的电源完整性”,在设计con, 2018。[4] L. Smith和E. Bogatin, PDN设计的电源完整性原则。普伦蒂斯大厅,2017年。

“电力配电网设计方法的比较”,2006。

[4] H. Barnes和S. Sandler,“平Z PCB配电网络的解耦电容优化”2018年IEEE电磁兼容性和信号/电源完整性研讨会(EMCSI)。

[5] S. Sandler,“如何设计电源完整性”Keysight赞助的YouTube视频系列:http://www.keysight.com/find/how-to-videos-for-pi.