各种共面波导(CPW)的结构已经在过去的研究。例如,CPW是温在1969年提出的[1],b[2]。Gupta在[3]中列出了各种类型的CPW:有限介电厚度的CPW,有限接平面的CPW,带屏蔽层的CPW,带屏蔽层的导体背CPW,多层CPW,非对称CPW和有限介电厚度共面波导(CBCPW)。Wolff在b[4]中分析了CPW。最近,人们对5G应用[5]、高速数字应用[6]-[9]和光学频率[10]的毫米波频率下PCB和集成电路上传输线的宽带特性重新产生了兴趣。具体的传输线特征已经被研究,从铜粗糙度建模[11],[12],在CPW中放置过孔[12]- [18],CPW的性能已经与[19]中的微带进行了比较。

带状线是高速数字电路中首选的传输线。带状线的优点是它支持TEM模式,因此没有色散,也没有较低的截止频率。带状线具有低辐射,此外,远端串扰为零,因为对称产生相对电容和电感耦合近似等于[20]。然而,对于特定的传输线阻抗,信号带的宽度与基板的高度必须是固定的,这限制了带线的设计灵活性。

CPW的一个优点是它的设计灵活性。cpw可以在厚基板上制造。在CPW中实现特定特性阻抗的设计准则是信号带宽度与间隙的比值。(信号带的宽度与基板的高度之比不需要固定就能产生50欧姆的线路。)只要间隙尺寸小于衬底厚度[1],特性阻抗与衬底厚度无关。为了避免寄生微带模式,微带的宽度和间隙必须小于到下或上地的距离。为了避免带状线模式,间隙必须小于信号线宽度。

在带状线和CPW中都可以引入过孔以防止平行板波导模式,但这会增加制造复杂性和成本。此外,可以引入气桥来消除槽线(即奇数CPW)模式。CPW可以制成比微带[21]更小的尺寸,因此,带状线也是如此。为了使平行板模式最小化,可以减小与信号线在同一层上的接平面的尺寸,使结构成为有限接地共面波导(FGC)。

在实践中,基板的底部通常是金属化的,用于结构支撑和改善多层板中各层之间的隔离。顶部的金属盖也存在于封装电路中,使得大多数CPW结构都是带盖屏蔽的导体背压CPW。这项工作研究了嵌入式导体支持的CPW,具有覆盖屏蔽和有限尺寸的接地FGC,适用于多层板,如英特尔架构平台[22]。本文研究了带线和带屏蔽线的FGC的损耗比较、模态分析和耦合问题。

仿真设置

首先利用HFSS的模态分析对FGC和带状线进行了单线模拟。对于单线,为CPW和带状线设置了四种模式,长度为4mil。然后使用HFSS解嵌功能将结果解嵌到1英寸。

在模拟中使用了FR-4板的典型值:r= 4:4, tan = 0:02 = 5:78。采用HFSS中的Groiss模型[23]选项,粗糙度设为RMS=6 m。对所有金属表面设置相同的粗糙度。在这种情况下,CPW的性能很可能被低估了,因为在信号带的一侧,电场集中的地方,粗糙度较低。所有金属的有限厚度为1/ 20z,或t = 0:7密耳。介质损耗采用简单损耗模型进行建模。

带状线尺寸使用是德科技高级设计系统[24]中的Linecalc进行设计。衬底的尺寸最初使用的是典型的基于英特尔的多层板。在多层堆叠中,层是芯层、预浸料层和铜箔层。在本仿真中,介质材料为典型的FR4均质衬底,且芯和预preq具有相同的介电性能。带状线信号宽度设置为w= 7mils,到任何一个地的距离保持在9mils,以保持50欧姆的阻抗。

利用[26]和ADS中的方程,在Matlab[25]中计算具有屏蔽阻抗的导体背压CPW,将信号线宽度设置为7mils,并增加到地的距离,直到在衬底高度h=12mils处寄生微带模式最小化。CPW到地平面的距离设为16mils。对于50欧姆-欧姆线路,间隙为g = 4密耳。然后通过查看广义s参数来检查HFSS中的传输线阻抗模拟,以查看线路阻抗是否成功实现。

损失的表征

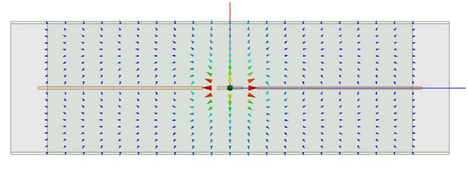

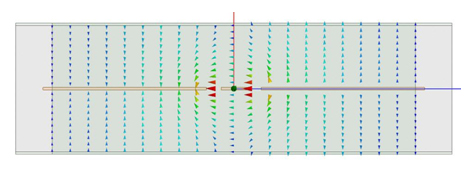

模拟的CPW和带状线模式如图1和2所示。在HFSS中模拟了所有模式的衰减和相位常数。CPW和带状线的主导模式具有较大的实际相位常数400radm和衰减常数(10ghz时为10 Np/m)。其他非主导模式在模拟中是消失的。

图1所示。偶(cpw)模式的向量表示。

图2。寄生槽线(奇)模式的矢量表示。

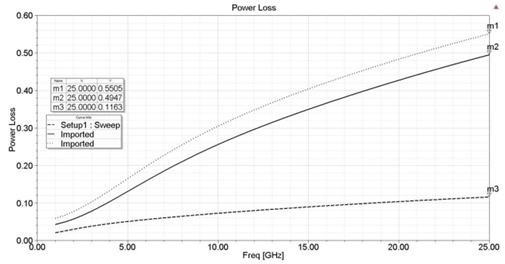

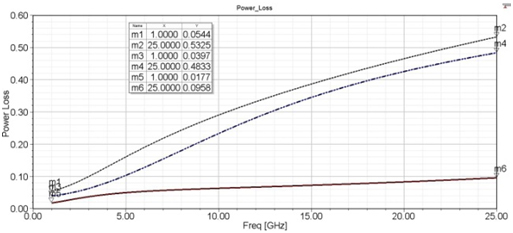

为了估计每种损耗对嵌入CPW的影响,我们依次加入铜的电导率、介电损耗和粗糙度,如图3和图4所示。这里使用了最坏的情况,假设所有信号和地面表面的粗糙度为6米。图表显示,当皮肤深度为粗糙度(0.1 GHz)量级时,粗糙度变得重要。为了公平地比较目标带宽的损耗,从总功率中减去插入损耗和回波损耗,如式1所示。介质损耗是总损耗的最大贡献者。

图3。损失对CPW损失的贡献。(a)欧姆损耗(b)欧姆和介电损耗(c)经济、介电和粗糙度。

图4。损失对CPW损失的贡献。(a)欧姆损耗(b)欧姆和介电损耗(c)经济、介电和粗糙度。

边缘耦合CPW和带状线的比较

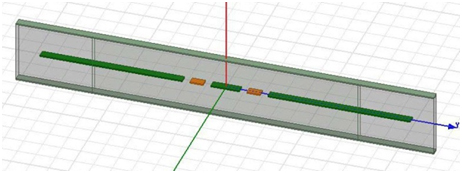

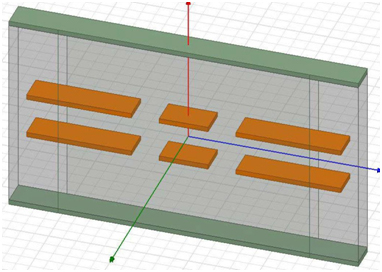

在本节中,模拟了两个边缘耦合的cpw和带状线,如图5所示。两条带状线之间的水平分离间隙以5mil的增量变化,从5mil到15mil不等。在CPW中,两个CPW之间的中心地面宽度在相同的距离内是不同的。采用终端仿真模拟4mils粗线段,其中有一个996mils脱嵌端口。波端口被分配到电路的正面和背面,如图5所示。选择波口的大小,使高阶模式,包括波导模式从波口不传播。选择上、下、侧地作为参考导线,在左、右中心导线和中地分别放置3个端子。侧地被指定为通过波端口边缘的地。中地终端重新规范为10个6指定另一个接地导体,并将中心导体重新标准化为50欧姆。CPW和未耦合带状线均为50欧姆,回波损耗大于30dB。

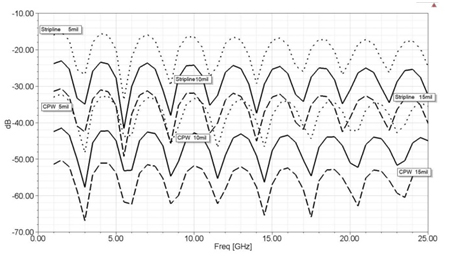

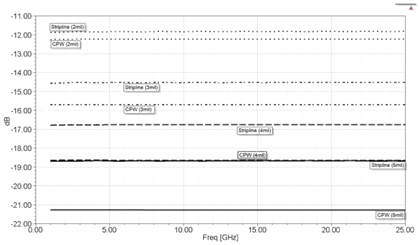

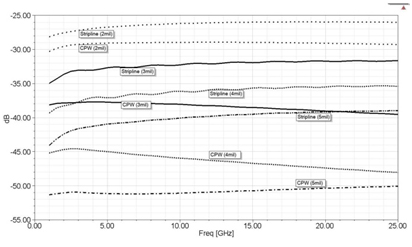

在所有配置中,CPW的性能都明显优于带状线,如图6和7所示。图6和图7中的虚线表示隔5mil的边耦合导体的隔离和耦合,实线表示隔10mil,虚线表示隔15mil。顶部虚线表示带状线,底部虚线表示CPW。可以显著增加共面CPW线的密度,以产生与带状线相同的耦合和隔离。例如,两个相距5mils的边耦合cpw的耦合与两条相距15mils的带状线的耦合相同。通过减小间隙宽度,可以进一步减小CPW中的耦合,从而将电场更紧密地限制在间隙[27]附近。

图5。边缘耦合CPW线。

图6。两条边耦合CPW和带状线的耦合比较。

图7。两个边缘耦合CPW和带状线的隔离比较。

舷侧耦合CPW与带状线比较

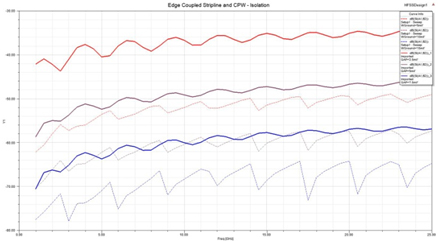

图8显示了两个宽侧耦合的cpw,并在类似的配置下模拟了带状线。利用HFSS的终端仿真对电路进行了仿真。两侧耦合线之间的距离分别为4,6和8mil。图9和图10中的标签显示了对称轴、x-y平面和每条线之间的距离。模拟以与上一个类似的方式进行,除了这一次,只有输入端口被去嵌入并重新规范化为50欧姆。输出波口未进行重归一化,呈现出完美的匹配条件,s参数被归一化为频率相关的阻抗,以呈现隔离和耦合之间的明显区别。与前面的模拟一样,结果与恒定50欧姆仪器的测量结果不一致,但在两种情况下,更容易看出耦合和隔离之间的差异。CPW线的耦合和隔离比带状线低。如果线路不携带差分信号,这是有益的。

图8。宽侧耦合CPW线。

图9。两个宽侧耦合带状线和cpw的耦合。

图10。两宽侧耦合带状线和cpw的隔离。

结论

在高速数字电路中,最大限度地减少信号层数,限制层转换,并消除带状线中的隔离接地层,以减少层数,从而降低多层板的价格和重量。我们表明,与stirpline相比,具有盖屏蔽的嵌入式CPW具有更大的设计灵活性和更高的封装密度,具有相当的耦合和隔离性能。

参考文献

[10]温正平,“一种适用于非互易陀螺磁器件的共面波导表面条形传输线”,中华民国微波学术研讨会论文集,第110-115页。

b[2]——,“共面波导:一种适用于非互易陀螺磁器件的表面条形传输线”,《IEEE微波理论与技术汇刊》,第17卷,第17期。12,第1087-1090页,1969。

K. Gupta,微带线和槽线,ser。Artech公司的天线和传播库。Artech House, 1996年。(在线)。可用:https://books.google.com/books?id=gqeHQgAACAAJ

[10]吴志强,共面微波集成电路。John Wiley & Sons, 2006。

[10] J. Coonrod,“毫米波频率下的电路材料管理”,微波学报,vol. 58, no. 10。7, pp. 98 - +, 2015。

[10]陈晓明,“高速数字应用的多层共面波导”,2002年IEEE mtts微波研讨会论文集,第2卷。

[10]郭晓明,陈建军,陈建军,“基于表面粗糙度的带状线互连信号传输分析”,电子工程学报,vol. 56, no. 10。3,第707-714页,2014。

[10]郭志刚,“共面波导测试装置在高速数字电路中的应用”,电子学报,vol. 29, no. 10。第22页,1939-1941年,1993。

[10]钱英杰,“皮秒脉冲在悬浮共面波导中的模态色散控制与畸变抑制”,《微波理论与技术学报》,vol. 40, no. 10。第10卷,1903-1909页,1992年。

[10]吴国强,吴国强,“基于直流-太赫兹频谱的低损耗低色散传输线”,《太赫兹科学技术学报》,vol. 6, no. 10。4, pp. 611-618, 2016。

[10]胡晓明,胡晓明,胡晓明,叶晓明,“一种表面粗糙度功率损耗的三维雪球模型”,《计算机工程学报》,2007。2007年SPI。IEEE研讨会。IEEE,会议论文集,第121-124页。

[10]王晓明,“基于多通道接地的共面波导互连技术研究”,电子工程学报,第6卷,第1期。1, pp. 136-144, 2016。

[10] W. H. Haydl,“在导体支持的共面电路中使用过孔”,《IEEE微波理论与技术汇刊》,vol. 50, no. 10。6,第1571-1577页,2002。

[10]张晓明,张晓明,张晓明,“三维集成中硅通孔和共面波导的射频表征和分析建模”,电子工程学报,第33卷,第1期。4, 2010年第1 - 4页。

[10]张志强,张志强,“基于栅极的微波封装技术”,中国科学院国际微波学术研讨会论文集(ei)。《会议论文集》第3卷,第1831-1834页,第3卷。

[10]王晓明,王晓明,等。金属表面粗糙度对导体背衬共面波导的影响研究。亚利桑那大学,2015年。

[10] A. Sain和K. L. Melde,“通过降低计算复杂度表征导体表面粗糙度对cb-cpw行为的影响”,2012年IEEE第21届电子封装与系统电气性能会议,会议论文集,pp. 260-263。

[10]余明,黄建军,“同轴发射器和圆片探头激励的比较研究”,微波学报,1993。, IEEE MTT-S国际。IEEE,会议论文集,第705-708页。

[10]刘建军,“微带与cpw性能的比较”,《微波学报》,第55卷,第1期。7, pp. 74-86, 2012。

[10] E. Bogatin,信号完整性:简化。Prentice Hall Professional, 2004。

[10] T. Sporkmann,“过去30年共面模的演变”,微波学报,欧洲-全球版,第41卷,第1期。7,第96-96、98、102、108、111页,1998。(在线)。可用地址:https://inspec:6049621

[10]刘建军,“基于集成电路的集成电路设计”,电子工程学报,2008。

[10]郭志强,“有耗腔谐振器的数值分析”,硕士论文,1996。

b[24] a.d系统,2016年发布。圣罗莎,加州:Keysight, Inc., 2016。

[25] MATLAB, 9.2.0版本(R2017a)。马萨诸塞州纳蒂克:The MathWorks Inc., 2017。

[10] R. N. Simons,“共面波导电路、元件与系统”。2001年。”

[10] G. Garcia和C. Chang,“两个共面波导之间的串扰”,美国海军海洋系统中心,1989。

本文最初发表于EDI CON USA 2018。