近年来,PCB互连中数字信号的频率含量增加到40-50 GHz。为了确保互连在这个带宽上按预期工作,我们必须建立验证板。本文报告了从验证项目中获得的经验教训,目标是建立一个系统预测高达40 GHz互连行为的正式程序。我们将讨论测试结构、连接器和测量设备的选择,展示基于初始制造前假设的分析的不确定性,并分析基于识别材料模型和制造商调整的更正式的方法如何更接近现实。

如何设计具有高达40 GHz的良好分析-测量相关性的PCB互连?是否可以通过典型的低成本PCB材料和制造工艺,典型的痕迹宽度,通过背钻和空间不足放置拼接孔?您的EDA供应商显示了分析工具与测量的良好相关性,即使高达50 GHz,您的PCB制造商确保板将按照设计建造,并提供有关堆叠和材料的所有可能信息。使用易于使用的TDNA或VNA进行测量也应该是“小菜一碟”。没有什么可担心的,设计的互连应该像预期的那样工作。

不幸的是,许多SI工程师很快就意识到事实并非如此,现实可能与我们的预期相差甚远。为了在这个频段上验证设计到制造流程中的几乎所有内容,我们实际上被迫建立验证板。此外,每次使用新的PCB材料,甚至是新一批材料或PCB制造商时,都必须进行重新验证。这种验证的结果应该是一个正式的过程,在此之后,我们减少了期望和现实之间的差距,并能够可靠地预测生产板上的互连行为在这个带宽上。这是这个项目的主要目标。我们不像在一些验证项目中通常做的那样,仅仅在个案的基础上显示最终的分析到测量的相关性,而是报告一个基于材料模型和制造调整识别的正式程序。分析并报告了基于制造前假设的分析的准确性。我们还讨论了在电路板设计、制造和测量中遇到的意想不到的工件(我们都知道,事情会发生)。

我们从描述“梦想验证项目”开始——如果一切都按照预期进行,验证过程应该是什么样的。作为框架,我们使用了“沉浮”验证流程,该流程由多个验证板开发和测试,如Teraspeed的PLRD-1 [1], Wild River Technology的CMP-08和CMP-28[2],[3],以及Rambus的“经验教训”板[4]。本文所描述的项目可以被认为是“沉或游”方法在与生产板结构接近的板上应用的第一份详细报告。

我们继续进行验证板计划,并讨论测试结构的选择。除了单端和差分传输线段用于材料参数识别和Beatty标准等测试结构外,该板还包括常见的高速PCB互连结构,如交流耦合电容器、延迟匹配补偿、DDR电路中使用的弯曲线、不同数量拼接孔的差分和单端通孔,用于研究能量局部化现象。正如通常所做的那样,所有结构都是根据PCB制造商提供的堆叠几何和材料参数设计的(制造前假设)。

接下来,我们展示了基于制造商提供的数据的模型的带宽是非常有限的。实际上,对于目标频率带宽,仅使用制造前的假设是不可能预测互连行为的。为了增加预测带宽和提高准确性,对过程的最小可能调整是什么?首先,我们用截面来验证轨迹的几何形状。通过一些横截面样本,我们做出了新的假设,即确定的痕迹宽度和形状调整对整个板来说是共同的。接下来,我们为每个信号层使用两个传输线段(单端和差分),用gms参数[5]正确识别材料模型。最后,基于有限的板截面和仅t线段的s参数测量,我们采用一组新的制造后假设,逐个结构进行分析,并将改进后的模型与测量值进行比较。这揭示了额外的预期和意料之外的惊喜。结果是一个相对简单的正式过程,为那些想要为验证项目和生产委员会设计可预测互连的人提供了一组建议。

“沉或游”验证过程

设计成功的关键要素之一是对制造、测量和建模进行系统的基准测试。系统意味着分析与测量的相关性,不仅观察到一个或两个结构(例如测试样板),而是广泛的典型互连-单端和差分,条带和微带,简单的平面和垂直过渡或通孔等。这样的比较应该在频率(s参数的幅度和相位)和时间(TDR和可选的眼图)域上一致地进行。换句话说,系统验证或基准测试是必要的,以确保电路板按设计制造,测量是正确的,最后,互连分析软件提供可接受的精度。这是一个巨大的项目,特别是如果你第一次做的时候没有太多的经验。幸运的是,有许多关于[1]-[4]类似项目的报道。这里我们将使用“沉或游”方法[4]作为基础。可分为7个步骤(包括电路板设计和制造):

1.与制造商一起选择材料并定义PCB堆叠

2.用EM分析设计测试结构(简单的链接,发射,通孔等)

3.制作单板并安装连接器

4.测量s参数,并通过正式的质量度量和视觉检查来验证测量的质量

5.横切电路板并确定生产调整(如果有的话)

6.利用gms参数或SPP Light技术识别宽带介质和导体粗糙度模型;

7.使用确定或验证的材料模型和确认的调整一致地模拟所有结构,并将s参数和TDR与测量结果进行比较(在此步骤中不允许对数据进行进一步的操作或“校准”);

最初的预期是在3个月内完成这个项目。说起来容易做起来难——由于优先级低、资源少,这个项目花了大约一年的时间才完成,我们仍在调查数据,为下一次迭代做准备。这个项目的主要障碍实际上是测量设备。不幸的是,关于什么测量设备适用于极宽带SI问题,什么不适合的知识并不是常识,供应商也并不总是很有帮助。

验证板设计

验证平台是非常重要的工具,可以对制造商进行资格预审,对信号完整性软件进行基准测试,或学习如何在微波到毫米波带宽范围内进行测量。通过对一组典型的互连结构进行分析-测量比较,可以很容易地确定该软件的准确性和局限性。验证平台可以自行开发,也可以从供应商处购买。业界首创的验证平台之一是Teraspeed咨询集团[1]的物理层参考设计板(PLRD-1)。PLRD-1的使用揭示了在Simbeor软件中开发行业首个宽带介质和导体粗糙度模型的必要性。

一个现成的验证平台的例子是[3]中介绍的Wild River Technology公司的CMP-28/32通道建模平台。现成的验证平台是学习的方便工具,但这种平台中的堆叠和互连几何可能不具有生产板的代表性。在这种情况下,必须使用具有类似于生产板的堆栈结构的自定义验证平台,就像在本项目中所做的那样。

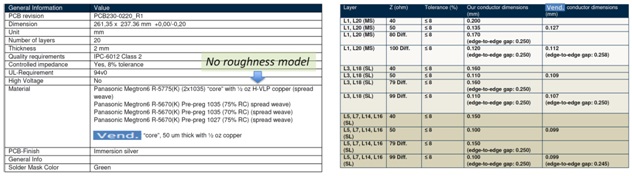

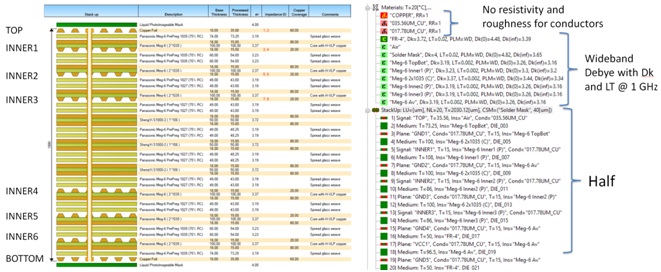

板的设计从材料的选择和堆叠的定义开始。高速布线层选用松下Megtron6材料。图1所示为电路板制造商提供的一些预制造规格。该板有20层,其中8层为高速信号,如图2所示。目标阻抗已经为PCB制造商指定,制造商必须用一些公差来实现它。这是生产板的通常选择。制造商提供了预期的轨迹宽度和间距调整,如图1右表所示。预期阻抗变化在8%以内,这太大了,期望在40 GHz有良好的相关性,但这是典型值。在板布局中用0.20mm (7.9 mil)衬垫的过孔将用0.250mm直径的钻头(9.85 mil)钻孔。不允许在任何层的信号通道上安装无功能的衬垫。 Via backdrilling is to be done for some structures.

图1。从制造商处获得的验证板材料和迹线宽度及调整。

图2。验证板堆叠(左)和Simbeor软件中的初始材料模型(右)。

预布局分析的Stackup定义如图2右侧所示。这是我们现阶段能做的最好的了。Megtron6规格提供介电常数和损耗正切在多个频率。预期宽带德拜(又名Djordjevic-Sarkar)模型定义的任何点从规格提供了一个很好的近似的目标频率带宽。主要问题在于导体粗糙度模型:我们所知道的是铜箔粗糙度指定为H-VLP,没有其他数据。PCB制造商在电路板制造过程中也会对铜箔的光亮面进行粗糙处理,没有任何电气建模参数。即使我们从铜箔制造商那里获得了铜箔的配对面数据,PCB制造商对闪亮面的处理使它实际上毫无用处。因此,我们开始时没有导体粗糙度模型,并使用PCB制造商提供的轨迹调整。显然,这将不能为插入损失提供良好的相关性,并且需要模型识别-这应该是预期的。不过,这些数据对于发射孔和过孔的设计是可以接受的。 Ideally, a test coupon with the same stackup should be built for the material identification, to identify the conductor surface roughness model, and to improve accuracy of the pre-layout analysis. The validation board may be considered as such coupon.

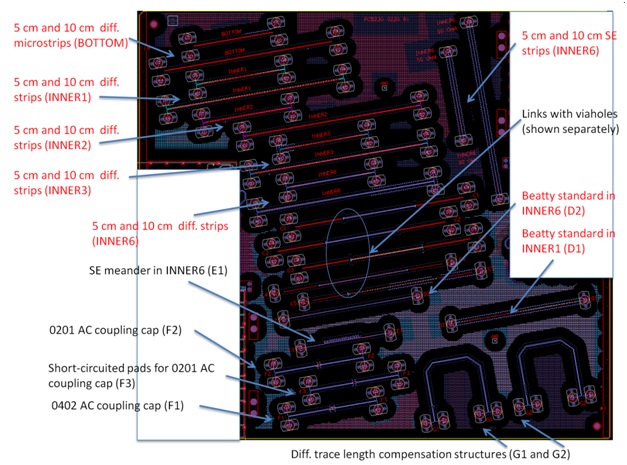

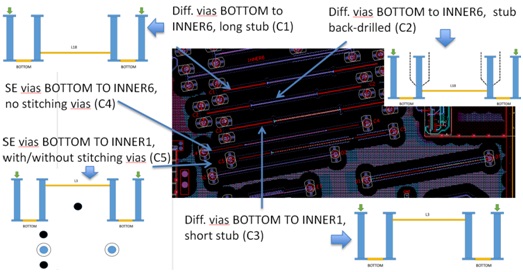

验证板上的结构应包括用于材料模型识别和验证的结构。为了使用gms参数[5]或SPP Light[6]进行识别,必须为每个唯一层使用两段差分或单端t线。此外,我们可以使用Beatty标准(串联谐振器)来确认提取的模型适用于不同宽度的迹线。用于材料识别的线段也可用于简单差动和单端链接的测试(它们类似于生产板上使用的迹线)。此外,我们决定将通常用于串行和并行接口的互连结构:每个路由层的差分和单端(SE)通孔;类似于SERDES链路上使用的交流耦合电容器;类似于DDR链路上使用的弯曲线段;以及差动连杆偏斜补偿结构。所有的路由在一个角度的边缘板,以避免纤维编织效果。所有结构的最终板布局如图3和图4所示。

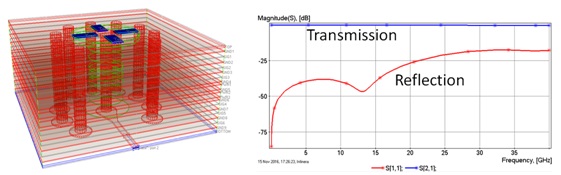

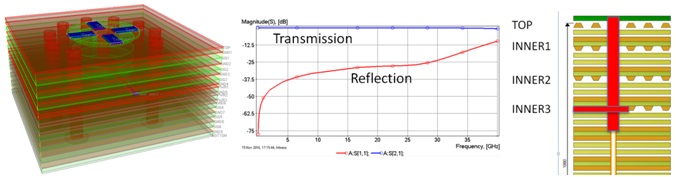

验证板设计中最重要的元素是发射。探针或连接器的启动都必须进行优化。如果发射反射太多,通常会使它们更容易受到制造变化的影响,并且更难以去嵌入以进行材料识别。设计目标是使反射和对制造变化的敏感性最小化。该板被设计为有2.92或2.4毫米压缩安装连接器安装在顶层。使用了来自两个供应商的连接器。设计了5个低反射孔,用于连接带有微带线的结构的TOP和BOTTOM, TOP到INNER1(带背钻),TOP到INNER2(带背钻),TOP到INNER3(带背钻),TOP到INNER6(不带背钻)。从制造商获得的堆栈/材料用于模拟和优化发射。

发射设计示例如图5和图6所示。发射是使用没有连接器的分解方法进行模拟和优化的——它降低了模型的质量,而且模型预计只能工作到30 GHz。所有发射都设计有9个缝合孔位于直径2.3毫米(91密尔)的圆上。拼接孔将所有参考平面与TOP层中的金属贴片连接在一起。拼接孔直径为0.250 mm (9.85 mil)。从信号通孔到拼接通孔的距离在30 GHz时约为波长的四分之一(介电介质中波长的四分之一约为1.35 mm) -预计发射应该在30 GHz左右逐渐失去定位(短路通孔在四分之一波长距离处的阻抗变得非常高,接近开放)。我们不能期望在这个频率以上有良好的相关性。尽管如此,由于大的平行平面和沿着t线段放置的大量拼接孔,预计返回路径的阻抗将保持低。

图3。20层验证板布局(红色图例为材料识别结构)

图4。带有单端(SE)和差动通孔的连杆布局。

图5。用于微带结构的从上到下层发射设计-反射损耗在27 GHz以下为-20 dB,在40 GHz以下为-10 dB。

图6。INNER2层带状线结构的TOP到INNER3层发射设计-反射损耗在33 GHz以下为-20 dB,在40 GHz以下为-10 dB。

电路板设计好并发送给制造商后,我们注意到金属痕迹被放在TOP层,如图3所示。幸运的是,这并不重要,因为TOP层被固体金属平面与板上的所有痕迹隔离开来。在板子布局阶段的最后,我们做了如下的现实观察:

- 在布局文件中,通孔直径定义为0.2 mm (7.9 mil),但制造商应该使用0.25 mm (9.85 mil) -它应该在布局后分析中考虑到;

- PCB采用“阻抗控制”工艺制造-所有的走线宽度和间距都由PCB制造商调整,这也不反映在布局文件中,但应在布局后分析中考虑;

- 没有痕迹形状信息(对损失评估很重要);

- 没有关于阻焊板形状/参数的信息;

- 无导体粗糙度模型信息;

- 没有实际回钻的资料;

所有这些都使得后布局分析不准确,在目标频率上实际上无用。这主要是因为缺少导体粗糙度模型。预计HVLP粗糙度和制造商额外的铜处理会大大降低3-5 GHz以上的信号,但我们没有数据来评估这些额外的损失。在任何项目中,如果没有预先建立的测试券,并且材料和制造商完全相同,这应该是预期的。然而,制造商提供的介电参数和堆叠结构可能是可以接受的,以设计垂直过渡。

测量和gms参数提取

测量步骤的主要目标是在10 MHz到40 GHz范围内测量精确、高质量的s参数。考虑到制造的变化和发射的本地化,s参数应适用于提取无反射广义模态s参数(gms参数),用于30 GHz以下的材料参数识别[5]。实现这一目标是本项目的最具挑战性和最漫长的一步。

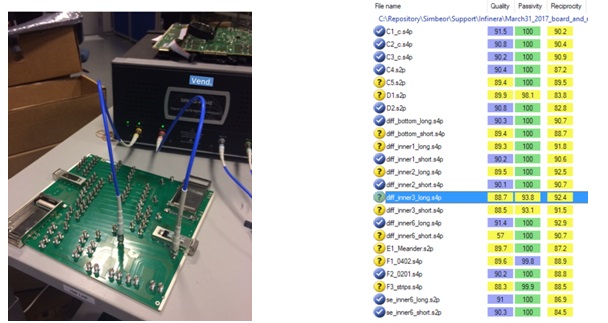

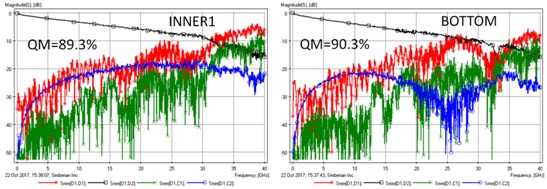

按计划制作板,先用TDNA测量s参数,如图7所示。这些s参数的正式质量指标勉强可以接受(如图7的右侧所示)。尽管如此,视觉检查显示,在图8中只有两个结构的s参数幅度图上可以清楚地看到大量的噪声。对于初步验证来说,这个噪音水平是可以接受的。但是,用这些s参数计算的gms参数[5]也有很大的噪声,如图9所示。我们面临着一个选择,要么继续处理这些嘈杂的数据,要么找到其他选择。

图7。使用TDNA的s参数测量设置(左)和最终的Simbeor质量度量(右,IEEE T370 PG3)。

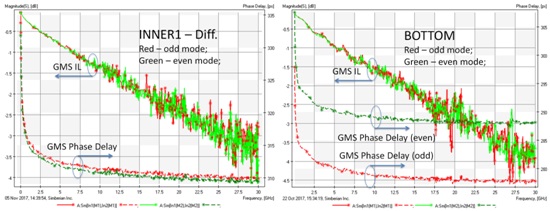

图8。示例:用TDNA测量层INNER1(条带,左)和层BOTTOM(微带,右)中差分10厘米段的混合模式s参数-可接受的质量指标,但有噪声。

图9。在INNER1层(左)和5厘米差分微带线(右)中,用TDNA测量的s参数计算出的gms参数可达10 GHz。

如果我们继续使用有噪声的gms参数,在10 GHz以上的材料识别将是模糊的。这是不可接受的。因此,我们决定寻找其他测量选项,包括尝试使用26 ghz VNA、多个40 ghz VNA和50 ghz VNA。